# Application of Silicon Dioxide (SiO<sub>2</sub>) Thin Films in Semiconductor Manufacturing

Author: BenchChem Technical Support Team. Date: December 2025

Application Note AP-SM-SIO2-001

### Introduction

Silicon dioxide (SiO<sub>2</sub>) is a cornerstone material in the semiconductor industry, prized for its excellent insulating properties, thermal stability, and the high-quality interface it forms with silicon.[1] This document provides a detailed overview of the primary applications of SiO<sub>2</sub> thin films in semiconductor manufacturing, along with experimental protocols for their deposition and characterization.

# **Key Applications of SiO<sub>2</sub> Thin Films**

Silicon dioxide films are integral to numerous steps in the fabrication of integrated circuits. Their primary roles include:

- Gate Dielectric: In Metal-Oxide-Semiconductor Field-Effect Transistors (MOSFETs), a thin layer of SiO<sub>2</sub> acts as the gate insulator, controlling the flow of current in the transistor channel. The quality of this layer is paramount for device performance and reliability.

- Device Isolation: SiO<sub>2</sub> is used to electrically isolate individual transistors on a chip, preventing cross-talk and parasitic device formation.[2] Key isolation techniques include Local Oxidation of Silicon (LOCOS) and Shallow Trench Isolation (STI).[3][4]

- Passivation Layer: A layer of SiO<sub>2</sub> can be deposited to protect the semiconductor surface from moisture, contamination, and mechanical damage during subsequent processing steps and packaging.

- Interlayer Dielectric (ILD): In multi-level metallization schemes, SiO<sub>2</sub> films are used to insulate the different layers of metal interconnects.

- Masking Layer: Due to its resistance to certain etchants and dopant diffusion at high temperatures, SiO<sub>2</sub> is an effective mask for patterning underlying layers.[1]

# Data Presentation: Properties of SiO<sub>2</sub> Thin Films

The required properties of SiO<sub>2</sub> films vary depending on their specific application. The following tables summarize key quantitative data for different deposition methods and applications.

Table 1: Electrical and Physical Properties of SiO<sub>2</sub> Thin Films

| Property                     | Thermal SiO₂<br>(Dry<br>Oxidation) | PECVD SiO₂<br>(TEOS) | ALD SiO₂         | Typical<br>Value/Range |

|------------------------------|------------------------------------|----------------------|------------------|------------------------|

| Dielectric<br>Constant (k)   | ~3.9[5]                            | 4.1 - 4.9[6]         | 4.0 - 7.5[7][8]  | Dimensionless          |

| Breakdown<br>Voltage (MV/cm) | >10[9]                             | 7 - 8.5[10]          | ~10.5[7][8]      | MV/cm                  |

| Refractive Index (@633nm)    | ~1.46[11]                          | ~1.45[12]            | ~1.45 - 1.52[13] | Dimensionless          |

| Density (g/cm³)              | 2.27                               | 2.1 - 2.3            | 2.2              | g/cm³                  |

Table 2: Typical SiO<sub>2</sub> Film Thickness for Various Applications

| Application                    | Typical Thickness Range | Notes                                                                           |  |

|--------------------------------|-------------------------|---------------------------------------------------------------------------------|--|

| Gate Dielectric (MOSFET)       | 1.5 - 10 nm             | Thinner for advanced nodes,<br>though high-k dielectrics are<br>now common.[14] |  |

| Tunneling Oxide (Memory)       | 1 - 5 nm                | Used in non-volatile memory devices.                                            |  |

| Field Oxide (LOCOS)            | 300 - 600 nm            | Grown by wet oxidation for device isolation.[15]                                |  |

| Shallow Trench Isolation (STI) | 300 - 500 nm            | Fills etched trenches for isolation in modern devices.                          |  |

| Pad Oxide (LOCOS/STI)          | 10 - 50 nm              | A thin stress-relief layer grown before nitride deposition.[7]                  |  |

| Interlayer Dielectric (ILD)    | 100 - 1000 nm           | Thickness depends on the specific metallization level.                          |  |

| Passivation Layer              | 100 - 500 nm            | Provides protection for the completed device.                                   |  |

# **Experimental Protocols Deposition Methods**

This protocol describes the growth of a high-quality, thin SiO<sub>2</sub> layer for a MOSFET gate dielectric using a horizontal furnace.

#### Materials:

- P-type or N-type silicon wafer

- High-purity oxygen (O2) gas

- High-purity nitrogen (N2) gas

### Equipment:

- Horizontal oxidation furnace with temperature control (e.g., Lindbergh-Tempress 8500)[16]

- Quartz wafer boat

- Wafer handling tools

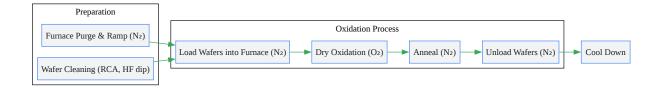

- Wafer Cleaning: Perform a standard RCA-1 and RCA-2 clean to remove organic and metallic contaminants from the wafer surface. A final dip in dilute hydrofluoric acid (HF) is used to remove the native oxide.

- Furnace Preparation: Purge the furnace tube with N<sub>2</sub> gas while ramping the temperature to the desired oxidation temperature (typically 900-1100°C).[17]

- Wafer Loading: Slowly push the wafer boat containing the silicon wafers into the center of the hot zone of the furnace under a continuous N<sub>2</sub> flow to prevent premature oxidation.[18]

- Oxidation: Switch the gas flow from N<sub>2</sub> to O<sub>2</sub>. The oxidation time will depend on the desired thickness, temperature, and crystal orientation of the silicon. For a 25 nm gate oxide at 1000°C, the oxidation time is approximately 1 hour.[16]

- Annealing (Optional): After oxidation, switch the gas back to N<sub>2</sub> and anneal the wafers at the oxidation temperature for 15-30 minutes. This step helps to improve the SiO<sub>2</sub>/Si interface quality.

- Wafer Unloading: Slowly pull the wafer boat to the end of the furnace tube under N2 flow.

- Cool Down: Allow the wafers to cool to room temperature before removal from the boat.

#### Thermal Oxidation Workflow

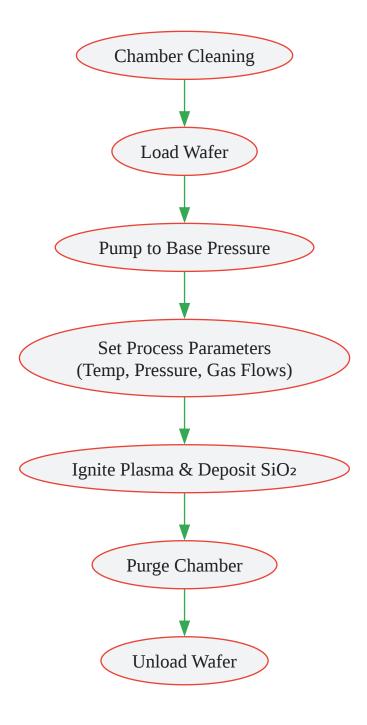

This protocol outlines the deposition of an SiO<sub>2</sub> film using a PECVD system with a tetraethyl orthosilicate (TEOS) precursor.

#### Materials:

- Substrate wafer (e.g., silicon)

- Tetraethyl orthosilicate (TEOS)

- Oxygen (O2) gas

- Nitrogen (N2) or Argon (Ar) gas

#### Equipment:

- PECVD system (e.g., Oxford PlasmaLab 100)[16]

- Vacuum pump

- Gas delivery system

#### Protocol:

• Chamber Preparation: Run a chamber cleaning recipe (e.g., O<sub>2</sub> plasma) to remove any residual films.

• Wafer Loading: Load the substrate onto the chuck in the PECVD chamber.

• System Pump Down: Evacuate the chamber to the base pressure.

• Process Conditions: Set the following process parameters (typical values):

Substrate Temperature: 250-400°C

o RF Power: 100-500 W

Pressure: 0.5-5 Torr

TEOS flow rate: 10-50 sccm

o O<sub>2</sub> flow rate: 200-1000 sccm

Deposition: Ignite the plasma and deposit the SiO<sub>2</sub> film for the calculated time to achieve the desired thickness. A typical deposition rate is 30-100 nm/min.[19]

- Post-Deposition Purge: After deposition, turn off the precursor and RF power, and purge the chamber with N<sub>2</sub> or Ar.

- Wafer Unloading: Vent the chamber and unload the wafer.

PECVD of SiO<sub>2</sub> Workflow

## **Device Isolation Protocols**

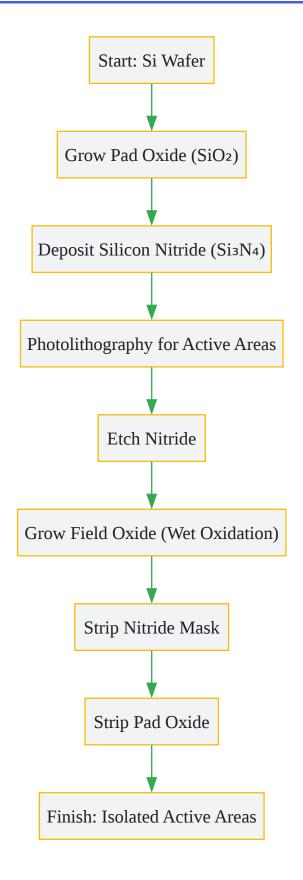

#### Protocol:

Pad Oxide Growth: Grow a thin layer of SiO<sub>2</sub> (pad oxide, 10-50 nm) on the silicon wafer via thermal oxidation.[7]

## Methodological & Application

- Nitride Deposition: Deposit a layer of silicon nitride (Si₃N₄, 100-200 nm) using LPCVD.[7]

- Photolithography: Spin-coat photoresist, expose it using a mask that defines the active areas, and develop the resist.

- Nitride Etch: Etch the Si₃N₄ layer in the exposed areas using reactive ion etching (RIE).

- Field Oxidation: Grow a thick SiO<sub>2</sub> layer (field oxide, 300-600 nm) in the areas where the nitride has been removed, typically using wet thermal oxidation. The Si<sub>3</sub>N<sub>4</sub> layer prevents oxidation in the active areas.[15]

- Nitride Removal: Strip the Si₃N₄ mask using hot phosphoric acid.

- Pad Oxide Removal: Remove the underlying pad oxide using a brief etch in dilute HF.

**LOCOS Process Flow**

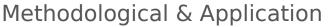

- Pad Layer Deposition: Deposit a pad oxide layer followed by a silicon nitride layer, similar to the LOCOS process.

- Photolithography: Pattern the wafer to define the isolation trench areas.

- Trench Etching: Etch the pad layers and the silicon substrate to a depth of 300-500 nm using RIE.

- Liner Oxidation: Grow a thin thermal oxide layer (liner oxide) on the trench sidewalls to repair any etch damage.

- Trench Fill: Deposit a thick layer of SiO<sub>2</sub> to completely fill the trenches, typically using a high-density plasma (HDP) CVD process.

- Chemical Mechanical Planarization (CMP): Use CMP to remove the excess SiO<sub>2</sub> from the surface, stopping on the nitride layer.

- Nitride Removal: Strip the nitride and pad oxide layers to reveal the isolated active areas.

Shallow Trench Isolation (STI) Workflow

## **Characterization Methods**

#### Equipment:

Spectroscopic ellipsometer

#### Protocol:

- System Calibration: Calibrate the ellipsometer using a reference silicon wafer.

- Sample Mounting: Place the SiO2-coated wafer on the sample stage.

- Measurement: Acquire the ellipsometric parameters (Psi and Delta) over a range of wavelengths and angles of incidence.

- Modeling: Create an optical model consisting of a silicon substrate and a SiO<sub>2</sub> layer (Cauchy model is often used for transparent films). For very thin oxides, an interface layer may be included in the model to improve accuracy.[20]

- Data Fitting: Fit the model-generated data to the experimental data by varying the thickness of the SiO<sub>2</sub> layer until a good fit is achieved. The software will then report the film thickness.

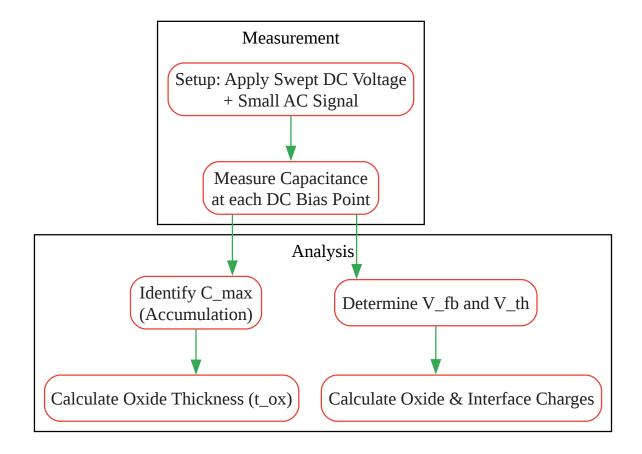

This protocol is for characterizing a MOS capacitor structure.

#### Equipment:

- C-V meter/Parameter analyzer (e.g., Keithley 4200A-SCS)[11]

- Probe station

- Device Fabrication: Fabricate a MOS capacitor by depositing a metal gate (e.g., aluminum) on top of the SiO<sub>2</sub> film and making a backside contact to the silicon wafer.

- Probing: Place the wafer on the probe station chuck (backside contact) and land a probe on the metal gate.

- Measurement Setup: Configure the C-V meter to sweep a DC voltage (e.g., from negative to positive for a p-type substrate) while applying a small, high-frequency AC signal (e.g., 1

MHz).[8]

- Data Acquisition: Perform the voltage sweep and record the capacitance at each DC bias point.

- Data Analysis:

- From the accumulation region (maximum capacitance), the oxide thickness (t\_ox) can be calculated.

- The flat-band voltage (V\_fb) and threshold voltage (V\_th) can be determined from the C-V curve, providing information about charges in the oxide and at the interface.[12]

Click to download full resolution via product page

C-V Measurement and Analysis Logic

## Wet Etching of SiO<sub>2</sub>

This protocol describes the removal of an SiO<sub>2</sub> layer using a buffered oxide etch (BOE) solution.

#### Materials:

- SiO<sub>2</sub>-coated wafer

- Buffered Oxide Etch (BOE) solution (e.g., 6:1 mixture of 40% NH<sub>4</sub>F in water to 49% HF in water)[21]

- Deionized (DI) water

- Plastic beakers and wafer carriers

#### Equipment:

- Wet bench with proper ventilation

- Timer

- Safety Precautions: Wear appropriate personal protective equipment (PPE), including acidresistant gloves, apron, and face shield. HF is extremely hazardous.

- Etch Time Calculation: Determine the required etch time based on the known etch rate of the BOE solution (e.g., ~70-100 nm/min for 6:1 BOE at room temperature) and the thickness of the SiO<sub>2</sub> film.[22][23]

- Etching: Immerse the wafer in the BOE solution for the calculated time. Gentle agitation can improve etch uniformity.

- Rinsing: Transfer the wafer to a DI water bath and rinse thoroughly to stop the etching process.

- Drying: Dry the wafer using a nitrogen gun.

Endpoint Detection (Visual): As the SiO<sub>2</sub> is removed, the silicon surface becomes hydrophobic. During the DI water rinse, a hydrophobic surface will cause the water to dewet, indicating the completion of the etch.[21]

#### **Need Custom Synthesis?**

BenchChem offers custom synthesis for rare earth carbides and specific isotopiclabeling.

Email: info@benchchem.com or Request Quote Online.

## References

- 1. SiO 2 thin film growth through a pure atomic layer deposition technique at room temperature - RSC Advances (RSC Publishing) DOI:10.1039/D0RA01602K [pubs.rsc.org]

- 2. ques10.com [ques10.com]

- 3. LOCOS Wikipedia [en.wikipedia.org]

- 4. m.youtube.com [m.youtube.com]

- 5. Thermal Oxidation [mks.com]

- 6. Buffered oxide etch Wikipedia [en.wikipedia.org]

- 7. dspace.mit.edu [dspace.mit.edu]

- 8. scientific-devices.com.au [scientific-devices.com.au]

- 9. researchgate.net [researchgate.net]

- 10. Vietnam: The ASEAN powerhouse | LSEG [Iseg.com]

- 11. download.tek.com [download.tek.com]

- 12. tek.com [tek.com]

- 13. ALD\_Recipes [seas.upenn.edu]

- 14. atlasti.com [atlasti.com]

- 15. web.stanford.edu [web.stanford.edu]

- 16. ECE Illinois ece444: Gate Oxidation Process [fabweb.ece.illinois.edu]

- 17. ate.community [ate.community]

- 18. lithoguru.com [lithoguru.com]

- 19. semitracks.com [semitracks.com]

- 20. przyrbwn.icm.edu.pl [przyrbwn.icm.edu.pl]

- 21. static1.squarespace.com [static1.squarespace.com]

- 22. filelist.tudelft.nl [filelist.tudelft.nl]

- 23. litho.nano.cnr.it [litho.nano.cnr.it]

- To cite this document: BenchChem. [Application of Silicon Dioxide (SiO<sub>2</sub>) Thin Films in Semiconductor Manufacturing]. BenchChem, [2025]. [Online PDF]. Available at: [https://www.benchchem.com/product/b107595#application-of-sio-thin-films-in-semiconductor-manufacturing]

#### **Disclaimer & Data Validity:**

The information provided in this document is for Research Use Only (RUO) and is strictly not intended for diagnostic or therapeutic procedures. While BenchChem strives to provide accurate protocols, we make no warranties, express or implied, regarding the fitness of this product for every specific experimental setup.

**Technical Support:**The protocols provided are for reference purposes. Unsure if this reagent suits your experiment? [Contact our Ph.D. Support Team for a compatibility check]

Need Industrial/Bulk Grade? Request Custom Synthesis Quote

# BenchChem

Our mission is to be the trusted global source of essential and advanced chemicals, empowering scientists and researchers to drive progress in science and industry. Contact

Address: 3281 E Guasti Rd

Ontario, CA 91761, United States

Phone: (601) 213-4426

Email: info@benchchem.com