# Application of Hafnium Silicide in Advanced CMOS Gate Stacks: Application Notes and Protocols

Author: BenchChem Technical Support Team. Date: December 2025

| Compound of Interest |                  |           |

|----------------------|------------------|-----------|

| Compound Name:       | Hafnium silicide |           |

| Cat. No.:            | B077831          | Get Quote |

For Researchers, Scientists, and Drug Development Professionals

# **Introduction: The Need for High-k Dielectrics**

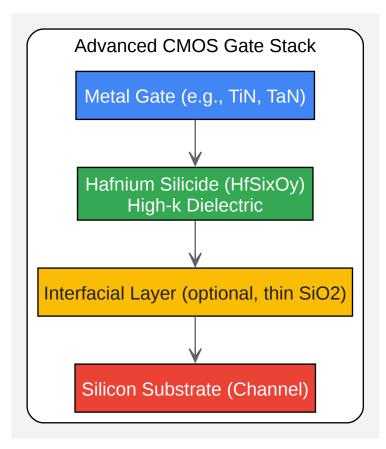

As complementary metal-oxide-semiconductor (CMOS) technology continues to scale down, the traditional silicon dioxide (SiO<sub>2</sub>) gate dielectric has reached its physical limits. Further reduction in SiO<sub>2</sub> thickness leads to unacceptably high gate leakage currents due to direct tunneling, resulting in increased power consumption and reduced device reliability.[1] To overcome this challenge, high-k dielectrics, materials with a higher dielectric constant than SiO<sub>2</sub>, are being integrated into advanced CMOS gate stacks. These materials allow for a physically thicker gate dielectric while maintaining the same capacitance, thereby reducing leakage current.[2]

Among various high-k candidates, hafnium-based materials, particularly hafnium oxide (HfO<sub>2</sub>) and **hafnium silicide** (HfSi $_{\times}$ O $_{Y}$ ), have emerged as the most promising replacements for SiO<sub>2</sub> due to their excellent thermal stability and electrical properties.[1][3] **Hafnium silicide**, in particular, offers several advantages over hafnium oxide, including a higher crystallization temperature and improved thermal stability when in direct contact with silicon.[4]

# **Properties and Advantages of Hafnium Silicide**

**Hafnium silicide** combines the high dielectric constant of hafnium oxide with the stable interface properties of silicon dioxide. The incorporation of silicon into hafnium oxide increases the material's band gap and crystallization temperature, making it more compatible with the high-temperature processes used in CMOS manufacturing.[3]

#### Key Advantages:

- Higher Thermal Stability: Hafnium silicate remains amorphous at higher temperatures compared to HfO<sub>2</sub>, which tends to crystallize during thermal annealing, leading to increased leakage current.[4]

- Reduced Leakage Current: The amorphous structure and larger physical thickness for a

given equivalent oxide thickness (EOT) significantly reduce gate leakage. For instance, a 50

Å HfSi<sub>×</sub>O<sub>Y</sub> film can exhibit a leakage current of 1.2×10<sup>-6</sup> A/cm<sup>2</sup> at 1 V bias.[5][6]

- Tunable Properties: The electrical and physical properties of **hafnium silicide**, such as its dielectric constant and band gap, can be tuned by varying the silicon concentration.[7][8]

- Improved Interface Quality: While most high-k materials struggle to form a high-quality interface with silicon, hafnium silicate demonstrates a stable interface with low defect density.

[9]

### **Data Presentation**

**Table 1: Comparison of Gate Dielectric Materials**

| Property                | Silicon Dioxide<br>(SiO <sub>2</sub> ) | Hafnium Oxide<br>(HfO <sub>2</sub> ) | Hafnium Silicide<br>(HfSi <sub>×</sub> O <sub>Y</sub> ) |

|-------------------------|----------------------------------------|--------------------------------------|---------------------------------------------------------|

| Dielectric Constant (k) | ~3.9                                   | ~21-25                               | ~6-14                                                   |

| Band Gap (eV)           | ~9.0                                   | ~5.7-5.8                             | ~5.8 - 7.0                                              |

| Crystallization Temp.   | Amorphous                              | ~400-500                             | >800 (amorphous with >13% Si even after 1000°C)[4]      |

Note: Properties of  $HfSi_{\times}O_{Y}$  can vary significantly with composition.[10]

Table 2: Effect of Silicon Content on Hafnium Silicide

**Properties**

| Silicon Content          | Dielectric Constant (k)                | Optical Band Gap (eV)                 |

|--------------------------|----------------------------------------|---------------------------------------|

| Low                      | Higher (approaching HfO <sub>2</sub> ) | Lower (approaching HfO <sub>2</sub> ) |

| High (e.g., 32 at. % Si) | ~4-5                                   | ~7.0                                  |

Data synthesized from multiple sources indicating the general trend.[7][8]

# Experimental Protocols Deposition of Hafnium Silicate Films

Several methods can be employed to deposit high-quality hafnium silicate films. The choice of method depends on the desired film properties and process integration requirements.

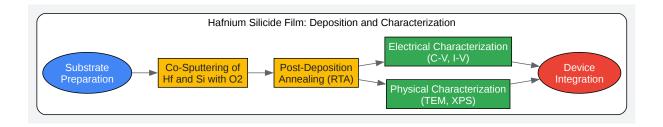

Protocol: Co-Sputtering of Hafnium and Silicon

This method allows for precise control over the film's stoichiometry by adjusting the power to the hafnium and silicon targets.

- Substrate Preparation:

- Start with a clean silicon wafer.

- Perform a standard RCA clean to remove organic and metallic contaminants.

- A final dip in dilute hydrofluoric acid (HF) is used to remove the native oxide and passivate the silicon surface with hydrogen.

- Sputter Deposition:

- Load the prepared wafer into a high-vacuum sputter deposition chamber.

- The chamber should be equipped with separate hafnium and silicon targets.

- Evacuate the chamber to a base pressure of <1x10<sup>−7</sup> Torr.

- Introduce high-purity argon (Ar) gas to a working pressure of a few mTorr.

- Apply DC or RF power to the silicon target and RF power to the hafnium target. The ratio of powers will determine the Hf:Si ratio in the film.

- During deposition, introduce a controlled flow of oxygen (O2) to form the silicate.

- The substrate can be heated (e.g., to 500°C) during deposition to improve film quality.[7]

- Post-Deposition Annealing (PDA):

- After deposition, the wafer is subjected to a rapid thermal anneal (RTA) in a nitrogen  $(N_2)$  or forming gas  $(H_2/N_2)$  ambient.

- Annealing temperatures can range from 450°C to 1000°C.[7][9] The higher temperatures

are used to test thermal stability.

#### **Characterization of Hafnium Silicate Films**

Physical Characterization:

- High-Resolution Transmission Electron Microscopy (HR-TEM): Used to examine the film's microstructure (amorphous or crystalline), thickness, and the quality of the interface between the hafnium silicate and the silicon substrate.[9]

- X-ray Photoelectron Spectroscopy (XPS): Determines the chemical composition and bonding states within the film, confirming the formation of Hf-O and Si-O bonds and the absence of undesired Hf-Si bonds.[9]

#### **Electrical Characterization:**

- Capacitance-Voltage (C-V) Measurements:

- Fabricate metal-insulator-semiconductor (MIS) capacitors by depositing metal electrodes

(e.g., gold or aluminum) on the hafnium silicate film.[9]

- Perform C-V measurements at various frequencies (e.g., 10 kHz to 1 MHz).[5]

- From the accumulation capacitance, the equivalent oxide thickness (EOT) can be calculated.

- The flatband voltage (Vfb) shift provides information about fixed charges in the dielectric.

Hysteresis in the C-V curve indicates the presence of trapped charges.[9]

- Current-Voltage (I-V) Measurements:

- Apply a voltage across the MIS capacitor and measure the resulting current to determine the gate leakage current density.[7]

- The breakdown field can also be determined from the I-V characteristics.[5][6]

# **Mandatory Visualizations**

Click to download full resolution via product page

Caption: Structure of an advanced CMOS gate stack featuring a **hafnium silicide** high-k dielectric.

Click to download full resolution via product page

Caption: Experimental workflow for the deposition and characterization of **hafnium silicide** films.

Click to download full resolution via product page

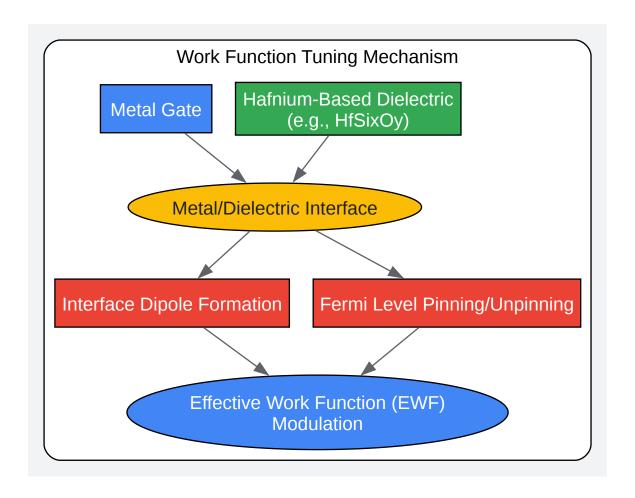

Caption: Logical relationship for work function tuning at the metal/high-k dielectric interface.

## **Application Notes**

- CMOS Scaling: The use of **hafnium silicide** as a gate dielectric is crucial for continued scaling of CMOS devices beyond the 45 nm technology node, enabling the fabrication of transistors with lower power consumption and higher performance.[11][12]

- Work Function Tuning: The effective work function of the metal gate, which determines the

transistor's threshold voltage, can be tuned by the choice of metal and by engineering the

interface with the hafnium-based dielectric. For instance, incorporating elements like

Lanthanum (La) into the gate stack can modulate the work function.[13] This is critical for

producing both n-type and p-type MOSFETs with the desired characteristics.

- Interfacial Layer Engineering: A thin interfacial layer of SiO<sub>2</sub> is often intentionally grown between the silicon substrate and the hafnium silicate.[3] This layer can improve the interface quality and channel mobility, but it also reduces the overall capacitance of the gate stack. Therefore, the thickness and quality of this interfacial layer must be carefully controlled.

- Challenges: Despite its advantages, challenges remain in the integration of **hafnium silicide**, including controlling the fixed charge density and minimizing interface traps to the level of the near-perfect SiO<sub>2</sub>/Si interface. Further research is focused on optimizing deposition processes and post-deposition treatments to mitigate these issues.

#### **Need Custom Synthesis?**

BenchChem offers custom synthesis for rare earth carbides and specific isotopiclabeling.

Email: info@benchchem.com or Request Quote Online.

# References

- 1. repositories.lib.utexas.edu [repositories.lib.utexas.edu]

- 2. api.repository.cam.ac.uk [api.repository.cam.ac.uk]

- 3. cityu.edu.hk [cityu.edu.hk]

- 4. researchgate.net [researchgate.net]

- 5. pubs.aip.org [pubs.aip.org]

- 6. ELECTRICAL PROPERTIES OF HAFNIUM SILICATE GATE DIELECTRICS DEPOSITED DIRECTLY ON SILICON | Semantic Scholar [semanticscholar.org]

- 7. pubs.aip.org [pubs.aip.org]

- 8. pubs.aip.org [pubs.aip.org]

- 9. pubs.aip.org [pubs.aip.org]

- 10. researchgate.net [researchgate.net]

- 11. scispace.com [scispace.com]

- 12. dr.ntu.edu.sg [dr.ntu.edu.sg]

- 13. [PDF] Tuning effective metal gate work function by a novel gate dielectric HfLaO for nMOSFETs | Semantic Scholar [semanticscholar.org]

- To cite this document: BenchChem. [Application of Hafnium Silicide in Advanced CMOS Gate Stacks: Application Notes and Protocols]. BenchChem, [2025]. [Online PDF]. Available at: [https://www.benchchem.com/product/b077831#application-of-hafnium-silicide-in-advanced-cmos-gate-stacks]

#### **Disclaimer & Data Validity:**

The information provided in this document is for Research Use Only (RUO) and is strictly not intended for diagnostic or therapeutic procedures. While BenchChem strives to provide accurate protocols, we make no warranties, express or implied, regarding the fitness of this product for every specific experimental setup.

**Technical Support:** The protocols provided are for reference purposes. Unsure if this reagent suits your experiment? [Contact our Ph.D. Support Team for a compatibility check]

Need Industrial/Bulk Grade? Request Custom Synthesis Quote

# BenchChem

Our mission is to be the trusted global source of essential and advanced chemicals, empowering scientists and researchers to drive progress in science and industry. Contact

Address: 3281 E Guasti Rd

Ontario, CA 91761, United States

Phone: (601) 213-4426

Email: info@benchchem.com