# Application Notes and Protocols for the Fabrication of Vertical GaN Power Devices

Author: BenchChem Technical Support Team. Date: December 2025

| Compound of Interest |                 |           |

|----------------------|-----------------|-----------|

| Compound Name:       | Gallium nitride |           |

| Cat. No.:            | B1216216        | Get Quote |

For Researchers, Scientists, and Professionals in Semiconductor and Materials Science

This document provides a detailed overview and experimental guidelines for the fabrication of vertical **Gallium Nitride** (GaN) power devices. The content is structured to provide a comprehensive understanding of the critical process steps, from substrate engineering to device fabrication and termination.

## **Introduction to Vertical GaN Power Devices**

**Gallium Nitride** (GaN) is a wide-bandgap semiconductor that is poised to revolutionize the power electronics industry.[1][2] Its superior material properties, including a high critical electric field, high electron mobility, and high thermal conductivity, enable the fabrication of power devices that are more efficient, smaller, and can operate at higher frequencies than their silicon-based counterparts.[3][4][5]

While lateral GaN devices have seen widespread commercial adoption, vertical device architectures are attracting increasing attention for high-power applications.[1][6] Vertical devices offer several advantages, including the ability to achieve higher breakdown voltages and current levels without increasing the chip size, and improved thermal management.[1][4][6] The peak electric field is also moved from the surface to the bulk of the material, enhancing reliability.[1][6]

The fabrication of high-performance vertical GaN devices is a complex process that involves several critical steps, each with its own set of challenges. This document will detail the key

techniques and protocols for substrate engineering, epitaxial growth, and device fabrication.

# **Substrate Engineering for Vertical GaN Devices**

The foundation of a high-quality vertical GaN device is the substrate. The ideal substrate has a low dislocation density and is closely lattice-matched to GaN. While native GaN substrates are the preferred choice, their high cost and limited availability have driven the development of alternative solutions.[6]

### **Bulk GaN Substrate Growth**

Homoepitaxy, the growth of GaN epitaxial layers on a GaN substrate, is the optimal approach for minimizing defects. Two primary methods are used for growing bulk GaN crystals: Hydride Vapor Phase Epitaxy (HVPE) and the Ammonothermal method.

- Hydride Vapor Phase Epitaxy (HVPE): This is the most common method for producing GaN substrates due to its high growth rate (exceeding 100 μm/h).[7][8] The process involves the reaction of gaseous metal chlorides with ammonia at high temperatures.[9] While costeffective, HVPE can result in a higher defect density compared to other methods.

- Ammonothermal Method: This technique is analogous to the hydrothermal growth of quartz, but uses supercritical ammonia as the solvent.[10][11] It is capable of producing very high-quality GaN crystals with low dislocation densities (on the order of 4.0 × 10<sup>4</sup> cm<sup>-2</sup>).[10] However, the growth rate is significantly lower than that of HVPE.[7]

Table 1: Comparison of Bulk GaN Growth Techniques

| Feature               | Hydride Vapor Phase<br>Epitaxy (HVPE) | Ammonothermal Method                   |

|-----------------------|---------------------------------------|----------------------------------------|

| Growth Rate           | >100 µm/h[7]                          | 2-10 μm/day[7][11]                     |

| Dislocation Density   | ~10 <sup>5</sup> cm <sup>-2</sup> [8] | ~10 <sup>4</sup> cm <sup>-2</sup> [10] |

| Operating Temperature | ~1045°C[12]                           | 400-600°C[10]                          |

| Operating Pressure    | < 1 atm[12]                           | 100-400 MPa[10]                        |

# **Alternative Substrates for Quasi-Vertical Devices**

To address the cost and size limitations of bulk GaN, significant research has focused on growing GaN on alternative substrates like silicon (Si), silicon carbide (SiC), and sapphire.[6] [13] These approaches lead to what are often termed "quasi-vertical" devices, where the current flows vertically through the epitaxial layers but the substrate itself may be removed or is not GaN.

- GaN-on-Si: This is a cost-effective approach, but the large lattice and thermal mismatch between GaN and Si presents significant challenges in managing stress and defects, limiting the thickness of the GaN layer that can be grown.[6][14]

- GaN-on-SiC: SiC is a better match to GaN in terms of lattice parameter and offers superior thermal properties. This makes it a promising substrate for high-power, high-frequency devices.[15]

- GaN-on-Sapphire: While sapphire is a cost-effective and insulating substrate, the large lattice mismatch with GaN leads to high defect densities.[13]

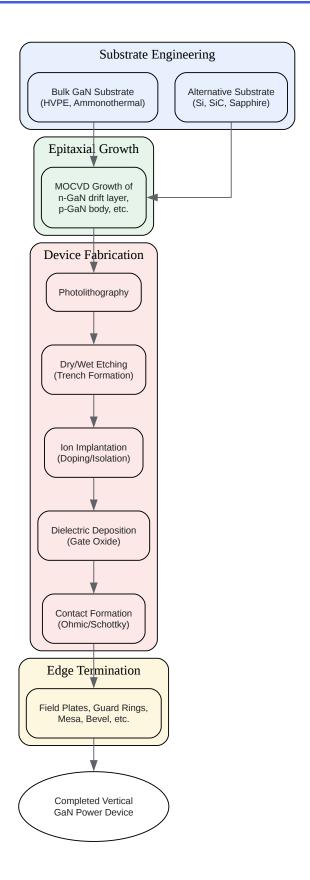

The overall workflow for producing vertical GaN devices, starting from substrate selection, is illustrated below.

Click to download full resolution via product page

Caption: High-level workflow for the fabrication of vertical GaN power devices.

# **Epitaxial Growth**

Once a suitable substrate is obtained, the active layers of the device are grown epitaxially. Metal-Organic Chemical Vapor Deposition (MOCVD) is the most common technique for the epitaxial growth of the complex multi-layer structures required for vertical GaN power devices. [6][16]

A typical epitaxial structure for a vertical GaN diode might consist of a highly doped n<sup>+</sup>-GaN bottom contact layer, a thick, lightly doped n<sup>-</sup>-GaN drift layer, a p-GaN layer, and a p<sup>+</sup>-GaN top contact layer.[3][6] The thickness and doping concentration of the drift layer are critical parameters that determine the breakdown voltage of the device.[6][17]

# Protocol for MOCVD Growth of a GaN Drift Layer

This protocol outlines a general procedure for the MOCVD growth of a lightly doped n-type GaN drift layer, which is a critical component for achieving high breakdown voltage.

#### 1. Substrate Preparation:

- Begin with a high-quality, low-dislocation density GaN substrate.

- Perform a solvent clean using acetone, methanol, and isopropanol, followed by a deionized water rinse.

- Perform an in-situ bake in the MOCVD reactor under a hydrogen atmosphere at >1000°C to remove surface contaminants.

#### 2. Growth Parameters:

- Precursors: Trimethylgallium (TMGa) for gallium, ammonia (NH₃) for nitrogen, and silane (SiH₄) for n-type doping.

- Carrier Gas: Hydrogen (H<sub>2</sub>) or a mixture of H<sub>2</sub> and Nitrogen (N<sub>2</sub>).

- Growth Temperature: 1000-1100°C.

- Reactor Pressure: 100-400 Torr.

- V/III Ratio (NH3/TMGa): >1000. A high V/III ratio is crucial for good crystal quality.

- SiH<sub>4</sub> Flow Rate: Adjusted to achieve the target doping concentration (e.g., 1x10<sup>16</sup> to 5x10<sup>16</sup> cm<sup>-3</sup>).[18]

#### 3. Growth Procedure:

- Introduce the carrier gas into the reactor.

- Ramp the substrate to the growth temperature.

- Introduce NH₃ to stabilize the GaN surface.

- Introduce TMGa and SiH4 to initiate growth.

- Continue growth until the desired drift layer thickness is achieved (e.g., 5-15 μm for >1.2 kV devices).[13][18]

- Terminate the TMGa and SiH4 flows.

- Cool down the reactor under an NH₃ and carrier gas ambient.

- 4. Characterization:

- Thickness: Measured using techniques like scanning electron microscopy (SEM) or ellipsometry.

- Doping Concentration: Determined by capacitance-voltage (C-V) measurements on a test structure.

- Crystal Quality: Assessed by X-ray diffraction (XRD) and atomic force microscopy (AFM).

## **Device Fabrication**

The fabrication of a vertical GaN device involves a series of standard semiconductor processing steps, including photolithography, etching, ion implantation, dielectric deposition, and metallization.

# **Trench Etching**

Trench structures are fundamental to many vertical GaN device architectures, including trench MOSFETs and trench-gated Schottky rectifiers.[1] The quality of the trench, particularly the smoothness of the corners, is critical to avoid electric field crowding and premature device breakdown.[1]

Table 2: Typical Parameters for GaN Trench Etching

| Parameter         | Value                                                       |

|-------------------|-------------------------------------------------------------|

| Etching Technique | Inductively Coupled Plasma - Reactive Ion Etching (ICP-RIE) |

| Etch Chemistry    | Cl <sub>2</sub> /BCl <sub>3</sub> /Ar[19]                   |

| ICP Power         | 300 - 800 W                                                 |

| RIE Power         | 50 - 200 W                                                  |

| Chamber Pressure  | 2 - 10 mTorr                                                |

| Mask Material     | SiO <sub>2</sub> or Ni                                      |

# Ion Implantation for Selective Doping and Isolation

Ion implantation is a key technology for creating selectively doped regions in vertical GaN devices, which is challenging to achieve through diffusion due to the high thermal stability of GaN.[20] It is used for forming p-type regions, n-type source/drain contacts, and for device isolation.[21][22] A significant challenge with p-type doping using Magnesium (Mg) implantation is the need for high-temperature annealing (>1300°C) to activate the dopants and repair lattice damage, which is above the decomposition temperature of GaN.

# **Edge Termination**

A critical aspect of high-voltage vertical GaN device design is the edge termination, which is necessary to manage the electric field at the device periphery and prevent premature breakdown.[23][24] Several techniques are employed, each with its own trade-offs between performance and fabrication complexity.[23]

- Field Plates (FP): These are metal extensions over a dielectric layer that help to spread the depletion region and reduce the peak electric field at the device edge.[3][23]

- Guard Rings (GR): These are floating p-n junctions surrounding the main device that help to distribute the reverse voltage.[24]

- Junction Termination Extension (JTE): This involves creating a region of precisely controlled charge at the device edge, typically through ion implantation, to shape the electric field.[25]

26

Mesa and Bevel Structures: These involve physically shaping the semiconductor to control the electric field distribution. [23]

Click to download full resolution via product page

Caption: Comparison of common edge termination techniques for vertical GaN devices.

# **Protocol for a Trench MIS Field Plate Edge Termination**

This protocol outlines the fabrication of a Trench Metal-Insulator-Semiconductor (MIS) Field Plate, an effective edge termination structure.[3]

- 1. Epitaxial Structure:

- Start with a wafer containing the p<sup>+</sup>/n<sup>-</sup>/n<sup>+</sup> diode structure. For a 1 kV device, the n<sup>-</sup> drift layer may have a doping of  $\sim$ 2.8 x 10<sup>16</sup> cm<sup>-3</sup> and a thickness of  $\sim$ 6.7  $\mu$ m.[3]

- 2. Trench Etching:

- Deposit a hard mask (e.g., SiO<sub>2</sub>) and pattern it using photolithography to define the trench area at the device periphery.

- Etch the trench into the n<sup>-</sup> drift layer using a Cl<sub>2</sub>-based ICP-RIE process. The trench depth is a critical design parameter.[3]

- 3. Dielectric Deposition:

- Thoroughly clean the wafer to remove any etch residues.

- Deposit a high-quality dielectric layer, such as SiO<sub>2</sub> or Al<sub>2</sub>O<sub>3</sub>, using Atomic Layer Deposition

(ALD) to ensure conformal coverage of the trench sidewalls and bottom.[27] The dielectric

thickness is another key design parameter.[3]

- 4. Field Plate Metallization:

- Use photolithography to define the field plate area. The field plate should extend from the anode contact, over the dielectric, and across the trench.

- Deposit the field plate metal (e.g., Ni/Au) using e-beam evaporation or sputtering.

- · Perform liftoff to remove the excess metal.

#### 5. Annealing:

Perform a post-metallization anneal in a nitrogen atmosphere to form good ohmic contacts and stabilize the dielectric interfaces.

## Conclusion

The development of vertical GaN power devices is a rapidly advancing field with the potential to significantly impact power electronics.[28][29] Success in this area requires a multi-disciplinary approach, encompassing materials science for substrate and epitaxial growth, and process engineering for device fabrication. The protocols and data presented in these notes provide a foundation for researchers and scientists to develop and optimize the next generation of high-performance vertical GaN power devices.

#### **Need Custom Synthesis?**

BenchChem offers custom synthesis for rare earth carbides and specific isotopiclabeling.

Email: info@benchchem.com or Request Quote Online.

# References

- 1. compoundsemiconductor.net [compoundsemiconductor.net]

- 2. Gallium Nitride: A Strategic Opportunity for the Semiconductor Industry [csis.org]

# Methodological & Application

- 3. Design of Trench MIS Field Plate Structure for Edge Termination of GaN Vertical PN Diode

PMC [pmc.ncbi.nlm.nih.gov]

- 4. Item High-Power Vertical GaN Electronic Devices Formed by Epitaxial Lift-Off -University of Notre Dame - Figshare [curate.nd.edu]

- 5. Gallium Nitride (GaN) STMicroelectronics [st.com]

- 6. research.unipd.it [research.unipd.it]

- 7. przyrbwn.icm.edu.pl [przyrbwn.icm.edu.pl]

- 8. researching.cn [researching.cn]

- 9. Hydride vapour-phase epitaxy Wikipedia [en.wikipedia.org]

- 10. sensors.myu-group.co.jp [sensors.myu-group.co.jp]

- 11. Growth of GaN crystals under ammonothermal conditions | MRS Online Proceedings Library (OPL) | Cambridge Core [cambridge.org]

- 12. nl3.unipress.waw.pl [nl3.unipress.waw.pl]

- 13. compoundsemiconductor.net [compoundsemiconductor.net]

- 14. 645 V quasi-vertical GaN power transistors on silicon substrates | IEEE Conference Publication | IEEE Xplore [ieeexplore.ieee.org]

- 15. Fabrication of Quasi-Vertical GaN-On-SiC Trench MOSFETs | Scientific.Net [scientific.net]

- 16. researchgate.net [researchgate.net]

- 17. mdpi.com [mdpi.com]

- 18. pubs.aip.org [pubs.aip.org]

- 19. researchgate.net [researchgate.net]

- 20. mdpi.com [mdpi.com]

- 21. Recent Progress of Ion Implantation Technique in GaN-Based Electronic Devices PMC [pmc.ncbi.nlm.nih.gov]

- 22. people.physics.anu.edu.au [people.physics.anu.edu.au]

- 23. mdpi.com [mdpi.com]

- 24. cpes.vt.edu [cpes.vt.edu]

- 25. A Simple Edge Termination Design for Vertical GaN P-N Diodes | IEEE Journals & Magazine | IEEE Xplore [ieeexplore.ieee.org]

- 26. researchgate.net [researchgate.net]

- 27. davidlu.net [davidlu.net]

- 28. Vertical GaN Power Devices: Device Principles and Fabrication Technologies—Part I |

IEEE Journals & Magazine | IEEE Xplore [ieeexplore.ieee.org]

- 29. Vertical GaN Power Devices: Device Principles and Fabrication Technologies—Part II |

IEEE Journals & Magazine | IEEE Xplore [ieeexplore.ieee.org]

- To cite this document: BenchChem. [Application Notes and Protocols for the Fabrication of Vertical GaN Power Devices]. BenchChem, [2025]. [Online PDF]. Available at: [https://www.benchchem.com/product/b1216216#techniques-for-creating-vertical-gan-power-devices]

#### **Disclaimer & Data Validity:**

The information provided in this document is for Research Use Only (RUO) and is strictly not intended for diagnostic or therapeutic procedures. While BenchChem strives to provide accurate protocols, we make no warranties, express or implied, regarding the fitness of this product for every specific experimental setup.

**Technical Support:** The protocols provided are for reference purposes. Unsure if this reagent suits your experiment? [Contact our Ph.D. Support Team for a compatibility check]

Need Industrial/Bulk Grade? Request Custom Synthesis Quote

# BenchChem

Our mission is to be the trusted global source of essential and advanced chemicals, empowering scientists and researchers to drive progress in science and industry. Contact

Address: 3281 E Guasti Rd

Ontario, CA 91761, United States

Phone: (601) 213-4426

Email: info@benchchem.com