# Application Notes and Protocols for Yttrium Silicate in High-k Dielectric Applications

Author: BenchChem Technical Support Team. Date: December 2025

Audience: Researchers, scientists, and professionals in materials science and semiconductor device fabrication.

Introduction: As semiconductor devices continue to scale down, traditional silicon dioxide (SiO<sub>2</sub>) gate dielectrics face fundamental limitations due to excessive leakage currents arising from quantum tunneling.[1][2][3] High-k dielectrics, materials with a higher dielectric constant than SiO<sub>2</sub>, are being extensively researched to replace SiO<sub>2</sub>.[4] These materials allow for the fabrication of physically thicker films with the same equivalent oxide thickness (EOT), thereby reducing leakage current while maintaining high capacitance.[4][5] Yttrium silicate (Y-Si-O) has emerged as a promising high-k candidate due to its desirable thermodynamic stability, suitable dielectric constant, and amorphous nature at typical processing temperatures.[5][6]

## **Key Properties of Yttrium Silicate**

Yttrium silicate offers a combination of electrical and physical properties that make it an attractive alternative to SiO<sub>2</sub> for gate dielectric applications. A summary of these properties is presented below, with comparisons to silicon dioxide and yttrium oxide.

| Property                         | Yttrium Silicate (Y-<br>Si-O)                                                             | Yttrium Oxide<br>(Y₂O₃)                               | Silicon Dioxide<br>(SiO <sub>2</sub> ) |

|----------------------------------|-------------------------------------------------------------------------------------------|-------------------------------------------------------|----------------------------------------|

| Dielectric Constant (k)          | ~12-14[1][5][6][7]                                                                        | ~13-18[1]                                             | 3.9                                    |

| Band Gap (Eg)                    | > 5.5 eV[8]                                                                               | ~5.5-5.7 eV[9][10][11]                                | ~9 eV                                  |

| Equivalent Oxide Thickness (EOT) | Can achieve < 1.1<br>nm[1][7][12]                                                         | Can achieve < 1.0 nm                                  | Scales with physical thickness         |

| Leakage Current<br>Density       | Significantly lower<br>than SiO <sub>2</sub> for the<br>same EOT.[5][13]                  | Lower than SiO <sub>2</sub> for the same EOT.[13][14] | High at thicknesses < 2 nm             |

| Fixed Charge Density             | ~9x10 <sup>10</sup> cm <sup>-2</sup><br>(negative)[6][15]                                 | Varies with deposition                                | Low                                    |

| Crystallization<br>Temperature   | Higher than many<br>metal oxides, remains<br>amorphous during<br>typical annealing.[5][6] | Can crystallize at relatively low temperatures.[5]    | Amorphous                              |

## **Experimental Protocols**

## Protocol 1: Deposition of Yttrium Silicate Thin Films via Oxidation of Sputtered Yttrium

This protocol describes the formation of yttrium silicate thin films by depositing a thin layer of yttrium metal onto a silicon substrate, followed by a high-temperature oxidation step. This process leverages the high reactivity of yttrium with both silicon and oxygen to form a stable silicate layer.[6][12]

#### Materials and Equipment:

- P-type Si(100) wafers (resistivity 0.1-0.3 Ω·cm)

- Sputtering system with a yttrium target

- Rapid thermal annealing (RTA) or tube furnace system

- High-purity N₂O gas

- Standard wafer cleaning reagents (e.g., RCA clean solutions)

#### Procedure:

- Substrate Cleaning:

- Perform a standard RCA clean on the Si(100) wafers to remove organic and metallic contaminants.

- Follow with a dilute hydrofluoric acid (HF) dip to remove the native oxide layer immediately before loading into the sputtering system.

- Yttrium Deposition:

- Transfer the cleaned Si wafer to the sputtering system.

- Deposit a thin film of yttrium (e.g., 2.5 nm) onto the silicon substrate.[6] The thickness of the initial yttrium layer will influence the final silicate thickness.[12]

- Silicide Formation (Optional but Recommended):

- Anneal the yttrium-coated wafer in a high-vacuum environment (e.g., 5 minutes) to form yttrium silicide.[6] This step can help in controlling the reaction between yttrium and silicon.

[12]

- Oxidation to Form Yttrium Silicate:

- Transfer the wafer to an RTA system or a tube furnace.

- Perform the oxidation step in a N<sub>2</sub>O atmosphere at a high temperature (e.g., 900°C) for a short duration (e.g., 15 seconds).[6][7] This step converts the yttrium silicide (or yttrium on silicon) into an amorphous yttrium silicate film.

Click to download full resolution via product page

Workflow for Yttrium Silicate Deposition.

## Protocol 2: Characterization of Yttrium Silicate Thin Films

This protocol outlines the key steps for characterizing the electrical properties of the fabricated yttrium silicate thin films, primarily through capacitance-voltage (C-V) measurements.

#### Materials and Equipment:

- · Yttrium silicate film on Si wafer

- Metal evaporation system (e.g., for Aluminum)

- Shadow mask for defining gate electrodes

- LCR meter (e.g., HP 4284A)

- · Probe station

- Tube furnace for post-metallization anneal (PMA)

#### Procedure:

- Fabrication of MOS Capacitors:

- On the backside of the wafer, evaporate a layer of Aluminum (~200 nm) to ensure good ohmic contact.[5]

- Using a shadow mask, evaporate metal dots (e.g., Aluminum) of a defined area on the surface of the yttrium silicate film to serve as the gate electrodes.

- Post-Metallization Anneal (PMA):

- Perform a forming gas anneal (e.g., 90% N<sub>2</sub> and 10% H<sub>2</sub>) at 400°C for 30 minutes.[5][7]

This step helps to improve the quality of the dielectric-semiconductor interface.

- Capacitance-Voltage (C-V) Measurement:

- Place the wafer on the probe station.

- Contact the top Al gate and the backside contact.

- Sweep the gate voltage from inversion to accumulation (e.g., -3V to +3V for p-type Si) at a high frequency (e.g., 1 MHz).[5][7]

- Record the capacitance as a function of the applied voltage.

- Data Analysis:

- From the C-V curve, extract the accumulation capacitance (C\_acc).

- Calculate the Equivalent Oxide Thickness (EOT) using the formula: EOT = (ε\_SiO<sub>2</sub> \* A) / C\_acc, where ε\_SiO<sub>2</sub> is the permittivity of SiO<sub>2</sub> and A is the area of the gate electrode.[5]

[16] Quantum mechanical corrections should be included for accurate EOT determination.

[5][7]

- Determine the flat-band voltage (V\_fb) from the C-V curve to estimate the fixed charge density in the dielectric film.[6][15]

Click to download full resolution via product page

Workflow for Electrical Characterization.

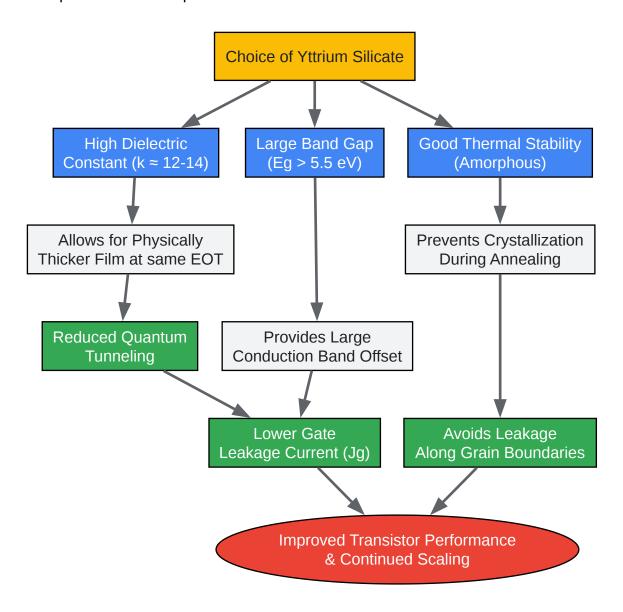

## Logical Relationships in High-k Dielectric Performance

The effectiveness of yttrium silicate as a high-k dielectric is rooted in the interplay of its fundamental material properties. The diagram below illustrates the logical flow from material choice to improved transistor performance.

Click to download full resolution via product page

Yttrium Silicate Properties to Performance.

#### **Need Custom Synthesis?**

BenchChem offers custom synthesis for rare earth carbides and specific isotopiclabeling.

Email: info@benchchem.com or Request Quote Online.

### References

- 1. researchgate.net [researchgate.net]

- 2. Equivalent oxide thickness Wikipedia [de.wikipedia.org]

- 3. Equivalent oxide thickness Wikipedia [en.wikipedia.org]

- 4. High-K Dielectric Materials for Transistors [atomfair.com]

- 5. pubs.aip.org [pubs.aip.org]

- 6. Physical and Electrical Properties of Yttrium Silicate Thin Films | MRS Online Proceedings Library (OPL) | Cambridge Core [cambridge.org]

- 7. chem.rutgers.edu [chem.rutgers.edu]

- 8. researchgate.net [researchgate.net]

- 9. researchgate.net [researchgate.net]

- 10. emdgroup.com [emdgroup.com]

- 11. mdpi.com [mdpi.com]

- 12. pubs.aip.org [pubs.aip.org]

- 13. researchgate.net [researchgate.net]

- 14. pubs.acs.org [pubs.acs.org]

- 15. Physical and Electrical Properties of Yttrium Silicate Thin Films | MRS Online Proceedings Library (OPL) | Cambridge Core [cambridge.org]

- 16. en.wikichip.org [en.wikichip.org]

- To cite this document: BenchChem. [Application Notes and Protocols for Yttrium Silicate in High-k Dielectric Applications]. BenchChem, [2025]. [Online PDF]. Available at: [https://www.benchchem.com/product/b1139545#yttrium-silicate-in-high-k-dielectric-applications]

#### **Disclaimer & Data Validity:**

The information provided in this document is for Research Use Only (RUO) and is strictly not intended for diagnostic or therapeutic procedures. While BenchChem strives to provide accurate protocols, we make no warranties, express or implied, regarding the fitness of this product for every specific experimental setup.

**Technical Support:**The protocols provided are for reference purposes. Unsure if this reagent suits your experiment? [Contact our Ph.D. Support Team for a compatibility check]

Need Industrial/Bulk Grade? Request Custom Synthesis Quote

## BenchChem

Our mission is to be the trusted global source of essential and advanced chemicals, empowering scientists and researchers to drive progress in science and industry.

#### Contact

Address: 3281 E Guasti Rd

Ontario, CA 91761, United States

Phone: (601) 213-4426

Email: info@benchchem.com