# Application Notes and Protocols for Tungsten Disulfide in Field-Effect Transistors

Author: BenchChem Technical Support Team. Date: December 2025

| Compound of Interest |                    |           |

|----------------------|--------------------|-----------|

| Compound Name:       | Tungsten disulfide |           |

| Cat. No.:            | B075915            | Get Quote |

For Researchers, Scientists, and Drug Development Professionals

This document provides detailed application notes and protocols for the utilization of **tungsten disulfide** (WS<sub>2</sub>) in the fabrication and characterization of field-effect transistors (FETs). These guidelines are intended to assist researchers in leveraging the unique electronic and physical properties of WS<sub>2</sub> for advanced electronic device applications.

## Introduction to Tungsten Disulfide (WS<sub>2</sub>) for Field-Effect Transistors

**Tungsten disulfide** (WS<sub>2</sub>) is a transition metal dichalcogenide (TMD) that has garnered significant interest for next-generation electronics due to its unique properties. As a semiconductor, WS<sub>2</sub> exhibits a layer-dependent bandgap, with a direct bandgap of approximately 2.1 eV in its monolayer form and an indirect bandgap of around 1.3 eV in its bulk form.[1][2] This tunable bandgap, combined with its atomically thin structure, high carrier mobility, and large on/off ratios in FETs, makes it a promising candidate for a variety of electronic and optoelectronic applications, including low-power logic circuits, sensors, and flexible electronics.[3][4][5][6]

Recent research has demonstrated high-performance WS<sub>2</sub> FETs with on/off ratios exceeding 10<sup>8</sup> and electron mobilities reaching up to 234 cm<sup>2</sup>/Vs at room temperature.[1][7][8] Achieving such high performance, however, is critically dependent on the quality of the WS<sub>2</sub> material, the fabrication process, and the engineering of interfaces, particularly the contacts. This document

outlines key considerations and protocols for fabricating and characterizing high-performance WS<sub>2</sub>-based FETs.

# **Key Performance Metrics of WS<sub>2</sub> Field-Effect Transistors**

The performance of WS<sub>2</sub> FETs is evaluated based on several key metrics. The following table summarizes typical performance parameters reported in the literature for both monolayer and multilayer WS<sub>2</sub> FETs.

| Performance Metric                 | Monolayer WS₂                   | Multilayer WS₂                                                     | Key<br>Considerations                                                                  |

|------------------------------------|---------------------------------|--------------------------------------------------------------------|----------------------------------------------------------------------------------------|

| Electron Mobility (μ)              | 10 - 115 cm²/Vs[4][9]           | Up to 234 cm²/Vs[1][7]<br>[8]                                      | Influenced by substrate, dielectric environment, defects, and contact resistance.[10]  |

| On/Off Current Ratio<br>(Ion/Ioff) | > 10 <sup>7</sup> [6]           | > 108[1][6][7][8][11]                                              | A high ratio is crucial for low-power switching applications.                          |

| Contact Resistance<br>(Rc)         | ~500 Ω·μm[12]                   | Varies significantly with contact metal and interface engineering. | Low contact<br>resistance is essential<br>for achieving high on-<br>state current.[12] |

| Subthreshold Swing (SS)            | Near-ideal values reported[12]  | Near-ideal values reported[12]                                     | Indicates the efficiency of switching the transistor from the off to the on state.     |

| On-State Current (Ion)             | > 600 μA/μm<br>(normalized)[12] | 280 μΑ/μm[ <b>11</b> ]                                             | Dependent on<br>mobility, contact<br>resistance, and gate<br>overdrive voltage.[12]    |

## **Experimental Protocols**

This section provides detailed protocols for the fabrication and characterization of back-gated WS<sub>2</sub> field-effect transistors.

## Protocol 1: Fabrication of WS<sub>2</sub> FETs using Mechanical Exfoliation

This protocol describes the fabrication of WS<sub>2</sub> FETs starting from bulk crystals using the micromechanical exfoliation technique.

#### Materials and Equipment:

- High-quality bulk WS2 crystals

- Heavily doped silicon wafers with a 300 nm thermal oxide layer (Si/SiO<sub>2</sub>)

- Scotch tape

- Optical microscope

- Atomic Force Microscope (AFM)

- · Electron Beam Lithography (EBL) system

- Thermal evaporator

- Semiconductor parameter analyzer

#### Procedure:

- Substrate Preparation: Clean the Si/SiO<sub>2</sub> substrate using a standard cleaning procedure (e.g., sonication in acetone, isopropanol, and deionized water).

- Mechanical Exfoliation:

- Press a piece of scotch tape onto the bulk WS<sub>2</sub> crystal.

- Repeatedly peel the tape apart to cleave the crystal into thinner layers.

- Gently press the tape with the exfoliated flakes onto the cleaned Si/SiO<sub>2</sub> substrate.

- Slowly peel off the tape, leaving behind WS<sub>2</sub> flakes of varying thicknesses on the substrate.

- Flake Identification and Characterization:

- Use an optical microscope to identify monolayer and few-layer WS<sub>2</sub> flakes based on their optical contrast.

- Confirm the thickness of the desired flakes using Atomic Force Microscopy (AFM) and Raman spectroscopy.[13]

- Device Patterning:

- Spin-coat a layer of EBL resist (e.g., PMMA) onto the substrate.

- Use an EBL system to define the source and drain contact patterns over the selected WS<sub>2</sub> flake.

- Metal Deposition:

- Develop the resist to create openings for the metal contacts.

- Deposit the contact metals (e.g., 3 nm Cr for adhesion followed by 50 nm Au) using a thermal evaporator.[14]

- Lift-off:

- Immerse the substrate in a suitable solvent (e.g., acetone) to lift off the remaining resist and excess metal, leaving behind the patterned source and drain electrodes.

- Annealing: Anneal the fabricated device in a forming gas (Ar/H<sub>2</sub>) or high vacuum at 200-300°C to improve the contact quality and remove residues.[1]

# Protocol 2: Fabrication of WS<sub>2</sub> FETs using Chemical Vapor Deposition (CVD)

This protocol outlines the fabrication of large-area WS<sub>2</sub> FETs using CVD-grown monolayer films.

#### Materials and Equipment:

- CVD furnace

- Tungsten oxide (WO₃) and sulfur (S) powders as precursors

- Growth substrate (e.g., sapphire or Si/SiO<sub>2</sub>)

- Poly(methyl methacrylate) (PMMA)

- Wet transfer setup (e.g., using KOH or HF solution)

- Standard photolithography or EBL equipment

- Reactive Ion Etching (RIE) system

- · Metal deposition system

- Semiconductor parameter analyzer

#### Procedure:

- CVD Growth of Monolayer WS<sub>2</sub>:

- Place the growth substrate in the center of the CVD furnace and the WO<sub>3</sub> powder upstream. Place the sulfur powder at a lower temperature zone.

- Heat the furnace to the desired growth temperature (typically 700-850°C) under an inert gas flow (e.g., Ar).

- Introduce the sulfur vapor to react with the WO₃ vapor, leading to the growth of monolayer

WS₂ on the substrate.

- Transfer of WS2 Film (if grown on a separate growth substrate):

- Spin-coat a layer of PMMA onto the WS<sub>2</sub>/growth substrate.

- Use a wet etching solution (e.g., hot KOH for sapphire) to separate the PMMA/WS<sub>2</sub> stack from the growth substrate.[15]

- Transfer the PMMA/WS2 film onto the target Si/SiO2 substrate.

- Remove the PMMA using acetone.

- Device Fabrication:

- Define the channel area by patterning the WS<sub>2</sub> film using photolithography or EBL followed by RIE with a plasma such as O<sub>2</sub> or SF<sub>6</sub>.[16][17]

- Pattern the source and drain contacts using a subsequent lithography step.

- Deposit the contact metals.

- Perform the lift-off process.

- Anneal the device to improve performance.

### **Protocol 3: Electrical Characterization**

#### Procedure:

- Place the fabricated device on the probe station of a semiconductor parameter analyzer.

- Output Characteristics (Ids-Vds):

- Apply a range of source-drain voltages (Vds) at a fixed gate voltage (Vgs).

- Repeat for several Vgs values to obtain a family of Ids-Vds curves.

- Transfer Characteristics (Ids-Vgs):

- Apply a small, constant Vds (e.g., 0.1 V or 1 V).

Sweep the Vgs from a negative to a positive voltage and measure the corresponding source-drain current (lds).

#### • Data Analysis:

- On/Off Ratio: Calculate the ratio of the maximum on-state current (Ion) to the minimum offstate current (Ioff) from the transfer curve.

- Field-Effect Mobility (μ): Calculate the mobility from the transconductance (gm = dlds/dVgs) in the linear region of the transfer curve using the formula: μ = [L / (W \* Cox \* Vds)] \* gm where L is the channel length, W is the channel width, and Cox is the gate oxide capacitance per unit area.

- Subthreshold Swing (SS): Determine the SS from the subthreshold region of the transfer curve (log scale) using the formula: SS = dVgs / d(log10lds)

## **Visualizations**

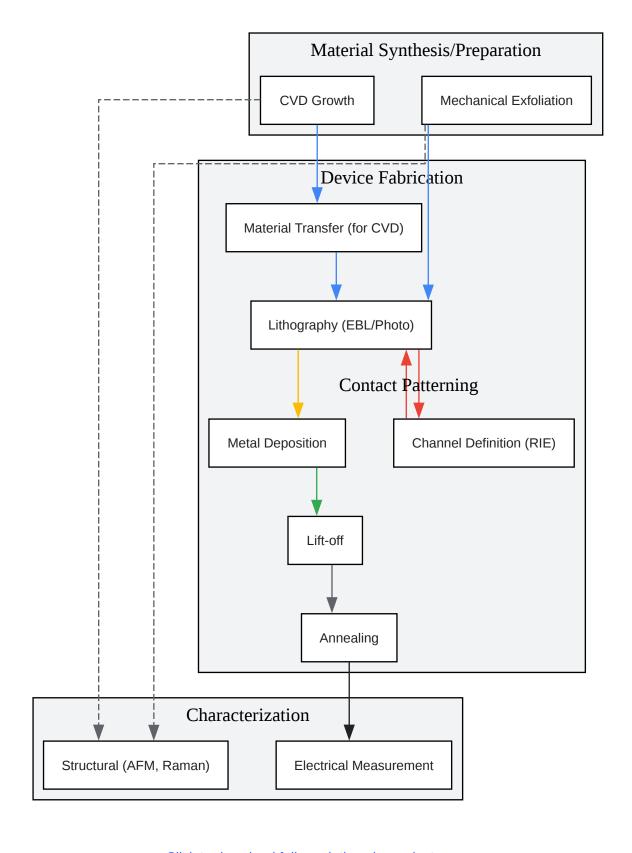

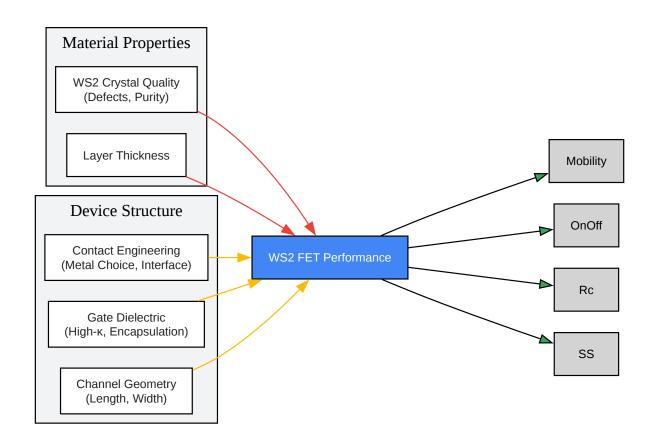

The following diagrams illustrate key workflows and concepts in the study of WS2 FETs.

Click to download full resolution via product page

Caption: General workflow for the fabrication and characterization of WS2 FETs.

Click to download full resolution via product page

Caption: Key factors influencing the performance of WS2 field-effect transistors.

#### **Need Custom Synthesis?**

BenchChem offers custom synthesis for rare earth carbides and specific isotopiclabeling.

Email: info@benchchem.com or Request Quote Online.

## References

- 1. arxiv.org [arxiv.org]

- 2. researchgate.net [researchgate.net]

- 3. researchgate.net [researchgate.net]

- 4. pure.psu.edu [pure.psu.edu]

- 5. mdpi.com [mdpi.com]

- 6. researchgate.net [researchgate.net]

- 7. High performance field-effect transistor based on multilayer tungsten disulfide PubMed [pubmed.ncbi.nlm.nih.gov]

- 8. pubs.acs.org [pubs.acs.org]

- 9. researchgate.net [researchgate.net]

- 10. arxiv.org [arxiv.org]

- 11. pubs.acs.org [pubs.acs.org]

- 12. IEEE Xplore Full-Text PDF: [ieeexplore.ieee.org]

- 13. researchgate.net [researchgate.net]

- 14. arxiv.org [arxiv.org]

- 15. researchgate.net [researchgate.net]

- 16. pubs.acs.org [pubs.acs.org]

- 17. Contact Resistance Engineering in WS2-Based FET with MoS2 Under-Contact Interlayer: A Statistical Approach - PMC [pmc.ncbi.nlm.nih.gov]

- To cite this document: BenchChem. [Application Notes and Protocols for Tungsten Disulfide in Field-Effect Transistors]. BenchChem, [2025]. [Online PDF]. Available at: [https://www.benchchem.com/product/b075915#using-tungsten-disulfide-in-field-effecttransistors]

#### **Disclaimer & Data Validity:**

The information provided in this document is for Research Use Only (RUO) and is strictly not intended for diagnostic or therapeutic procedures. While BenchChem strives to provide accurate protocols, we make no warranties, express or implied, regarding the fitness of this product for every specific experimental setup.

**Technical Support:** The protocols provided are for reference purposes. Unsure if this reagent suits your experiment? [Contact our Ph.D. Support Team for a compatibility check]

Need Industrial/Bulk Grade? Request Custom Synthesis Quote

## BenchChem

Our mission is to be the trusted global source of essential and advanced chemicals, empowering scientists and researchers to drive progress in science and industry. Contact

Address: 3281 E Guasti Rd

Ontario, CA 91761, United States

Phone: (601) 213-4426

Email: info@benchchem.com