# Application Notes and Protocols for Trimethylaluminum (TMA) in Thin Film Surface Passivation

Author: BenchChem Technical Support Team. Date: December 2025

| Compound of Interest |                   |           |

|----------------------|-------------------|-----------|

| Compound Name:       | Trimethylaluminum |           |

| Cat. No.:            | B3029685          | Get Quote |

Audience: Researchers, scientists, and drug development professionals.

### Introduction to Trimethylaluminum (TMA) for Surface Passivation

**Trimethylaluminum** (TMA), with the chemical formula Al(CH<sub>3</sub>)<sub>3</sub>, is a pyrophoric liquid widely used as a precursor in chemical vapor deposition (CVD) and, most notably, atomic layer deposition (ALD). In the context of materials science and semiconductor device fabrication, TMA is the primary aluminum source for depositing high-quality, ultra-thin films of aluminum oxide (Al<sub>2</sub>O<sub>3</sub>). These Al<sub>2</sub>O<sub>3</sub> films have demonstrated exceptional performance in the surface passivation of various materials, including silicon, III-V compound semiconductors, and perovskites.[1]

Surface passivation is a critical process that reduces the electronic activity of defects at a semiconductor's surface. These defects can act as recombination centers for charge carriers (electrons and holes), which is detrimental to the performance of electronic and optoelectronic devices like transistors and solar cells.[1] Effective passivation minimizes this recombination, leading to improved device efficiency and stability.[1]

Al<sub>2</sub>O<sub>3</sub> films grown from TMA provide excellent surface passivation through a combination of two mechanisms:

- Chemical Passivation: This involves the reduction of the density of interface traps (D<sub>it</sub>) by satisfying dangling bonds at the semiconductor surface.[1][2] For instance, at the crystalline silicon (c-Si) interface, an interfacial layer of silicon oxide (SiO<sub>x</sub>) is formed during deposition and subsequent annealing, which chemically passivates the surface.[3]

- Field-Effect Passivation: This mechanism is driven by a high density of fixed negative charges (Qf) within the Al<sub>2</sub>O<sub>3</sub> layer, typically on the order of 10<sup>12</sup> to 10<sup>13</sup> cm<sup>-2</sup>.[2][4] This built-in electric field repels minority carriers (electrons in p-type semiconductors) from the surface, effectively shielding them from the interface defects and thus reducing surface recombination.[1][4]

ALD is the preferred method for depositing these passivation layers due to its ability to produce highly conformal, uniform films with precise, atomic-level thickness control, even at low temperatures.[5][6]

# Application: Surface Passivation of Crystalline Silicon (c-Si)

The use of TMA to deposit Al<sub>2</sub>O<sub>3</sub> is a state-of-the-art passivation technique for both p-type and n-type silicon surfaces, widely adopted in the photovoltaic industry to produce high-efficiency solar cells.[2][7]

#### Signaling Pathway: ALD Chemistry for Al<sub>2</sub>O<sub>3</sub> Deposition

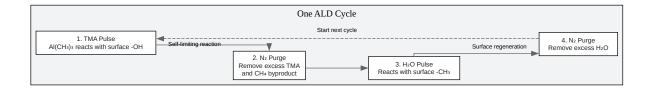

The thermal ALD process for  $Al_2O_3$  using TMA and water ( $H_2O$ ) is a binary reaction sequence. Each cycle consists of four steps:

- TMA Pulse: TMA is introduced into the reactor and reacts with the hydroxyl (-OH) groups on the substrate surface.

- Purge: Excess TMA and gaseous byproducts (methane, CH₄) are purged from the chamber with an inert gas like nitrogen (N₂).

- H<sub>2</sub>O Pulse: Water vapor is introduced and reacts with the surface-bound methyl (-CH<sub>3</sub>) groups.

Purge: Excess water and byproducts are purged, leaving a hydroxylated surface ready for the next cycle.

The overall reaction is:  $2AI(CH_3)_3 + 3H_2O \rightarrow AI_2O_3 + 6CH_4$ .[6]

Click to download full resolution via product page

Thermal ALD cycle for Al<sub>2</sub>O<sub>3</sub> using TMA and H<sub>2</sub>O.

#### Protocol 1: Thermal ALD of Al<sub>2</sub>O<sub>3</sub> on Crystalline Silicon

This protocol describes a typical thermal ALD process for depositing a 10 nm Al₂O₃ passivation layer on a p-type silicon wafer.

- 1. Substrate Preparation: a. Use p-type float-zone (FZ) <100> silicon wafers.[8] b. Perform a standard RCA clean or equivalent solvent clean to remove organic and metallic contaminants.

- c. To create a hydrogen-terminated surface, dip the wafers in a dilute hydrofluoric acid (HF) solution (e.g., 2% HF for 1 minute) immediately before loading into the ALD reactor. d. Rinse with deionized (DI) water and dry with a nitrogen gun.

- 2. ALD Process: a. Load the prepared wafers into the ALD reactor. b. Set the deposition temperature (Tdep) to between 100°C and 200°C. A lower temperature of 100°C can yield excellent results after annealing.[8] c. Set the TMA precursor source temperature to maintain sufficient vapor pressure (typically room temperature). d. Set the H<sub>2</sub>O precursor source temperature similarly. e. Execute the ALD cycles. For a growth rate of ~1.0-1.1 Å/cycle, approximately 90-100 cycles are needed for a 10 nm film.[8]

TMA pulse: 0.015 seconds.[8]

N<sub>2</sub> purge: 8 seconds.[8]

• H<sub>2</sub>O pulse: 0.015 seconds.[8]

• N<sub>2</sub> purge: 8 seconds.[8]

3. Post-Deposition Annealing: a. After deposition, transfer the wafers to a rapid thermal annealing (RTA) furnace or a conventional tube furnace. b. Anneal the samples in a nitrogen ( $N_2$ ) atmosphere for 5-10 minutes.[7][8] c. The optimal annealing temperature (Tann) is typically between 200°C and 400°C. An anneal at 200°C for 5 minutes has been shown to produce an effective carrier lifetime of 1 ms.[8]

**Data Presentation: TMA Passivation of Silicon**

| Parameter        | Value     | Substrate      | Outcome                                                                                          | Reference |

|------------------|-----------|----------------|--------------------------------------------------------------------------------------------------|-----------|

| Deposition Temp. | 100°C     | p-type FZ Si   | Growth per<br>cycle: 1.0 Å                                                                       | [8]       |

| Deposition Temp. | 150-200°C | p-type FZ Si   | Growth per<br>cycle: 1.1 Å                                                                       | [8]       |

| Film Thickness   | 10 nm     | p-type FZ Si   | Required for optimal chemical and field-effect passivation.                                      | [8]       |

| Annealing Temp.  | 200°C     | p-type FZ Si   | Effective carrier lifetime (teff): 1 ms.                                                         | [8]       |

| Annealing Temp.  | 200-300°C | p-type FZ Si   | Optimal range for overall surface passivation.                                                   | [8]       |

| Annealing Temp.  | ≥300°C    | p-type FZ Si   | Max negative fixed charge (Qox): $>3.0 \text{ x}$ $10^{12} \text{ cm}^{-2}$ .                    | [8]       |

| Annealing Temp.  | ≤250°C    | p-type FZ Si   | Min interface trap density ( $D_{it}$ ): $<3.0 \times 10^{10} \text{ eV}^{-1} \text{ cm}^{-2}$ . | [8]       |

| Deposition Temp. | 150°C     | p-type Si (p+) | Emitter saturation current (Joe): ~8 fA/cm².                                                     | [4]       |

# Application: Surface Passivation of III-V Semiconductors

III-V compound semiconductors like Gallium Arsenide (GaAs) and Indium Gallium Arsenide (InGaAs) suffer from poor native oxides that create a high density of interface states, pinning the Fermi level and limiting device performance. TMA pulses in an ALD process have been shown to effectively "clean up" these native oxides.[9][10]

### Logical Relationship: TMA "Clean-up" Effect on III-V Surfaces

The first few pulses of TMA in an ALD process can reduce the native oxides (e.g., Ga<sub>2</sub>O<sub>3</sub>, As<sub>2</sub>O<sub>3</sub>) on the III-V surface. This self-cleaning mechanism is crucial for forming a high-quality dielectric-semiconductor interface.[9]

TMA's effect on passivating III-V semiconductor surfaces.

#### Protocol 2: ALD of Al<sub>2</sub>O<sub>3</sub> on InGaAs

This protocol describes the deposition of Al<sub>2</sub>O<sub>3</sub> on an InGaAs surface for passivation.

- 1. Substrate Preparation: a. Use MBE-grown In<sub>0.15</sub>Ga<sub>0.85</sub>As/GaAs wafers.[10] b. No specific pre-cleaning (e.g., HF dip) is required, as the TMA will react with the native oxide layer formed during air exposure.[10]

- 2. ALD Process: a. Load the wafer into the ALD reactor. b. Set the deposition temperature to 300°C.[10] c. Set the chamber pressure to 1 Torr.[10] d. Execute the ALD cycles. The deposition rate is approximately 0.084 nm per cycle.[10][11]

- TMA pulse: 3 seconds.[10][11]

Ar purge: 3 seconds.[10][11]

H<sub>2</sub>O pulse: 3 seconds.[10][11]

Ar purge: 3 seconds.[10][11]

- 3. Characterization: a. The resulting interface can be characterized by X-ray Photoelectron Spectroscopy (XPS) to confirm the removal of arsenic oxides.[10] b. Electrical characterization of fabricated MOS capacitors can determine the interface trap density ( $D_{it}$ ), which can be reduced to ~10<sup>12</sup> eV<sup>-1</sup> cm<sup>-2</sup>.[10][11]

#### **Data Presentation: TMA Passivation of InGaAs**

| Parameter             | Value       | Substrate      | Outcome                                                               | Reference |

|-----------------------|-------------|----------------|-----------------------------------------------------------------------|-----------|

| Deposition Temp.      | 300°C       | Ino.15Gao.85As | Growth per cycle: 0.084 nm                                            | [10][11]  |

| Pulse/Purge<br>Times  | 3s/3s/3s/3s | Ino.15Gao.85As | Self-limited growth                                                   | [10][11]  |

| Passivation<br>Result | N/A         | Ino.15Gao.85As | Removal of arsenic oxides                                             | [10][11]  |

| Electrical Result     | N/A         | Ino.15Gao.85As | D <sub>it</sub> : ~10 <sup>12</sup> eV <sup>-1</sup> cm <sup>-2</sup> | [10][11]  |

| Leakage Current       | < 3 MV/cm   | Ino.15Gao.85As | 10 <sup>-8</sup> to 10 <sup>-9</sup><br>A/cm <sup>2</sup>             | [10][11]  |

# Application: Surface Passivation of Perovskite Solar Cells

In perovskite solar cells (PSCs), thin  $Al_2O_3$  layers deposited via ALD can act as effective passivation interlayers. They can reduce defect states at the perovskite surface, leading to improved open-circuit voltage ( $V_{\circ_c}$ ), fill factor (FF), and overall power conversion efficiency (PCE).[5] The deposition temperature is critical to avoid thermal degradation of the perovskite material.[5]

#### Protocol 3: ALD of Al<sub>2</sub>O<sub>3</sub> on MAPbl<sub>3</sub> Perovskite Films

- 1. Substrate Preparation: a. Fabricate the perovskite (e.g., MAPbI<sub>3</sub>) film on the desired substrate stack (e.g., FTO/TiO<sub>2</sub>). b. Immediately transfer the perovskite-coated substrate to the ALD reactor to minimize degradation from ambient exposure.

- 2. ALD Process: a. A low deposition temperature is crucial. 75°C has been identified as an optimal temperature to passivate the surface while minimizing perovskite degradation.[5] b. Use relatively small precursor exposures to avoid etching the perovskite.[5]

- TMA exposure: 0.025 Torr·s per cycle.[5]

- H<sub>2</sub>O exposure: 0.051 Torr·s per cycle.[5] c. Deposit a very thin layer (e.g., 5-20 cycles) of Al<sub>2</sub>O<sub>3</sub>.

- 3. Device Completion: a. Following ALD, deposit the hole transport layer (e.g., Spiro-OMeTAD) and the top metal contact (e.g., Au) to complete the solar cell.

### Data Presentation: TMA Passivation of Perovskite Solar Cells

| Deposition<br>Temp. | Perovskite | Change in<br>V <sub>oc</sub> | Change in<br>FF | Change in PCE            | Reference |

|---------------------|------------|------------------------------|-----------------|--------------------------|-----------|

| 75°C                | MAPbl₃     | Improved                     | Improved        | From 18.8%<br>to 20.0%   | [5]       |

| 125°C               | MAPbl₃     | N/A                          | N/A             | Drastic<br>deterioration | [5]       |

#### **Characterization Protocols**

Assessing the quality of surface passivation is critical. Below are brief overviews of key characterization techniques.

## Protocol 4: Measuring Effective Carrier Lifetime (τeff) with QSSPC

The Quasi-Steady-State Photoconductance (QSSPC) technique is a non-contact method to measure the effective minority carrier lifetime (teff) of a silicon wafer, which is a direct indicator of the level of recombination (both bulk and surface). Higher teff values indicate better passivation.

- 1. Sample Preparation: a. A symmetric sample structure is required, meaning the Al<sub>2</sub>O<sub>3</sub> passivation layer should be deposited on both sides of the wafer.[4]

- 2. Measurement: a. Place the passivated wafer in the QSSPC instrument. b. A flash lamp illuminates the sample, generating excess carriers, while a radio frequency coil measures the change in photoconductance. c. The instrument software calculates τeff as a function of the excess carrier density (injection level).

3. Data Interpretation: a. From  $\tau$ eff, the upper limit of the effective surface recombination velocity (Seff) can be calculated using the formula: Seff  $\leq$  W / (2 ×  $\tau$ eff), where W is the wafer thickness.[4] Lower Seff values signify better surface passivation.

### Protocol 5: Determining D<sub>it</sub> and Q<sub>ox</sub> with C-V Measurements

Capacitance-Voltage (C-V) and Conductance-Voltage (G-V) measurements on Metal-Oxide-Semiconductor (MOS) capacitor structures are powerful tools for quantifying interface quality.

- 1. Sample Preparation: a. Deposit the Al<sub>2</sub>O<sub>3</sub> passivation layer on the semiconductor wafer. b. Evaporate metal dots (e.g., Au or Al) through a shadow mask onto the Al<sub>2</sub>O<sub>3</sub> surface to form the top contacts of the MOS capacitors. c. Create a bottom contact on the backside of the wafer.

- 2. Measurement: a. Using a precision LCR meter, apply a sweeping DC bias voltage with a superimposed small AC signal to the MOS capacitor. b. Measure the capacitance and conductance at various frequencies (e.g., from 1 kHz to 1 MHz).

- 3. Data Interpretation: a. Fixed Charge ( $Q_{o\times}$ ): The flat-band voltage shift in the high-frequency C-V curve is used to calculate the density of fixed charges in the oxide. b. Interface Trap Density ( $D_{it}$ ): The frequency dispersion of the C-V curves in the depletion region or the peak in the conductance curve (from G-V measurements) can be used to extract the density of interface traps.[8][12]

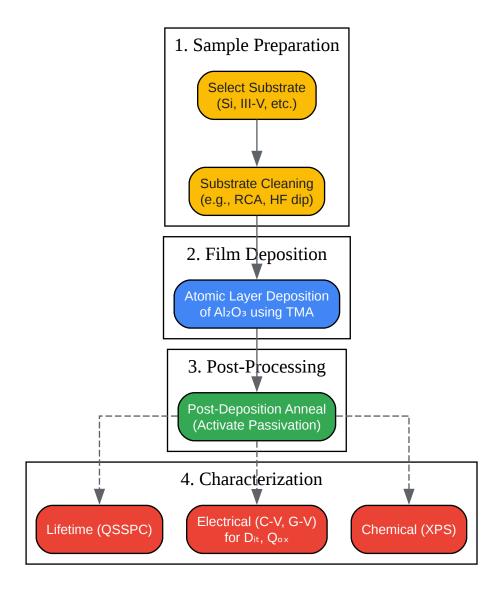

### **Experimental Workflow: From Passivation to Characterization**

Click to download full resolution via product page

General workflow for TMA-based surface passivation.

#### **Need Custom Synthesis?**

BenchChem offers custom synthesis for rare earth carbides and specific isotopiclabeling.

Email: info@benchchem.com or Request Quote Online.

#### References

- 1. Surface passivation as a cornerstone of modern semiconductor technology Highlighting a comprehensive review paper on surface passivation for silicon, germanium, and III–V materials – Atomic Limits [atomiclimits.com]

- 2. Passivation mechanism of thermal atomic layer-deposited Al2O3 films on silicon at different annealing temperatures PMC [pmc.ncbi.nlm.nih.gov]

- 3. pubs.acs.org [pubs.acs.org]

- 4. osti.gov [osti.gov]

- 5. Surface passivation of organometal halide perovskites by atomic layer deposition: an investigation of the mechanism of efficient inverted planar solar ... Nanoscale Advances (RSC Publishing) DOI:10.1039/D1NA00075F [pubs.rsc.org]

- 6. mdpi.com [mdpi.com]

- 7. researchgate.net [researchgate.net]

- 8. pubs.aip.org [pubs.aip.org]

- 9. researchgate.net [researchgate.net]

- 10. pubs.aip.org [pubs.aip.org]

- 11. pubs.aip.org [pubs.aip.org]

- 12. researchgate.net [researchgate.net]

- To cite this document: BenchChem. [Application Notes and Protocols for Trimethylaluminum (TMA) in Thin Film Surface Passivation]. BenchChem, [2025]. [Online PDF]. Available at: [https://www.benchchem.com/product/b3029685#using-trimethylaluminum-for-thin-film-surface-passivation]

#### **Disclaimer & Data Validity:**

The information provided in this document is for Research Use Only (RUO) and is strictly not intended for diagnostic or therapeutic procedures. While BenchChem strives to provide accurate protocols, we make no warranties, express or implied, regarding the fitness of this product for every specific experimental setup.

**Technical Support:** The protocols provided are for reference purposes. Unsure if this reagent suits your experiment? [Contact our Ph.D. Support Team for a compatibility check]

Need Industrial/Bulk Grade? Request Custom Synthesis Quote

#### BenchChem

Our mission is to be the trusted global source of essential and advanced chemicals, empowering scientists and researchers to drive progress in science and industry. Contact

Address: 3281 E Guasti Rd

Ontario, CA 91761, United States

Phone: (601) 213-4426

Email: info@benchchem.com