# Application Notes and Protocols for Tin-Based Semiconductors in Device Fabrication

Author: BenchChem Technical Support Team. Date: December 2025

| Compound of Interest |              |           |

|----------------------|--------------|-----------|

| Compound Name:       | Tin arsenide |           |

| Cat. No.:            | B12084615    | Get Quote |

A Research Guide to **Tin Arsenide** and Analogous Materials

For: Researchers, Scientists, and Drug Development Professionals

### Introduction

This document provides a detailed overview of the current state of research into **tin arsenide** (SnAs) for semiconductor device applications. Due to the limited availability of specific data and established protocols for **tin arsenide**, this guide also includes comprehensive application notes and experimental protocols for analogous, well-characterized tin-based and arsenide-based semiconductor materials. These protocols are intended to serve as a practical starting point for researchers interested in exploring the properties and potential applications of novel compound semiconductors.

Recent investigations into binary compounds have highlighted the diverse properties of materials within the tin-arsenide system. While initial interest may lie in the semiconducting properties of a simple SnAs stoichiometry, it is crucial to note that different phases possess varied electronic characteristics. For instance, the Sn4As3 phase has been reported to exhibit metallic properties, which would make it unsuitable for typical semiconductor device channel applications.[1] Research into nanocrystalline forms of SnAs with a cubic crystal structure has been reported, though comprehensive electronic characterization remains forthcoming.[2]

Given the nascent stage of research on **tin arsenide** for electronics, this document will leverage the extensive knowledge base of related materials to provide actionable protocols and

data. The following sections detail the material properties, synthesis methods, and device fabrication procedures for materials such as tin selenide (SnSe), tin oxide (SnO2), and gallium arsenide (GaAs) to serve as valuable analogues.

## Material Properties of Tin Arsenide and Analogous Semiconductors

A summary of the known properties of **tin arsenide** compounds is presented below, alongside key parameters for more established semiconductor materials. This data is essential for device design and fabrication, influencing everything from contact engineering to operational characteristics.

| Material                      | Crystal<br>Structure    | Lattice<br>Parameters<br>(Å)  | Band Gap<br>(eV)                     | Electron<br>Mobility<br>(cm²/V·s) | Hole<br>Mobility<br>(cm²/V·s) |

|-------------------------------|-------------------------|-------------------------------|--------------------------------------|-----------------------------------|-------------------------------|

| SnAs<br>(Nanocrystals<br>)    | Cubic (NaCl<br>type)[2] | Not Reported                  | Not Reported                         | Not Reported                      | Not Reported                  |

| Sn4As3                        | Trigonal<br>(R3m)[1]    | a = 4.089, c = 36.059[1]      | Metallic[1]                          | -                                 | -                             |

| Tin Selenide<br>(SnSe)        | Orthorhombic            | a=11.50,<br>b=4.15,<br>c=4.44 | ~0.9<br>(indirect),<br>~1.3 (direct) | Varies with doping                | Varies with doping            |

| Tin Dioxide<br>(SnO2)         | Tetragonal<br>Rutile    | a=4.738,<br>c=3.187           | ~3.6                                 | 100-200                           | Low                           |

| Gallium<br>Arsenide<br>(GaAs) | Zincblende[3]           | a = 5.653[4]                  | 1.42 (direct)<br>[3][5]              | up to 8500[6]                     | up to 400[6]                  |

## **Synthesis and Fabrication Protocols**

The following sections provide detailed protocols for the synthesis of semiconductor thin films and the fabrication of field-effect transistors (FETs) and photodetectors. While specific protocols

for **tin arsenide** are not yet established, these analogous procedures for related materials offer a robust methodological foundation.

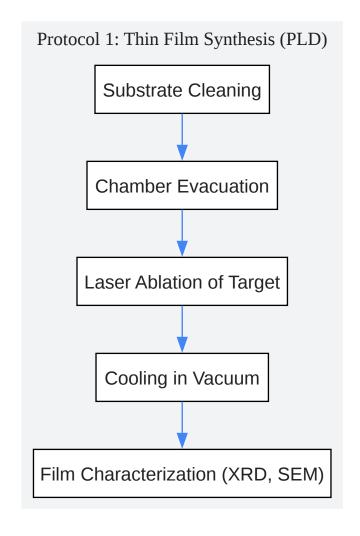

# Protocol 1: Thin Film Deposition by Pulsed Laser Deposition (PLD) - An Analogous Approach for Tin-Based Chalcogenides

Pulsed Laser Deposition is a versatile technique for growing high-quality thin films of various materials, including tin-based compounds like tin selenide.[7][8] This protocol is based on the synthesis of arsenic-doped tin selenide thin films.[7][8]

Objective: To deposit a crystalline, oriented thin film of a tin-based chalcogenide on a substrate.

### Materials and Equipment:

- Target material (e.g., hot-pressed SnSe or SnAs pellet)

- Substrate (e.g., Si/SiO2, quartz)

- Pulsed laser source (e.g., KrF excimer laser, λ = 248 nm)

- High-vacuum deposition chamber

- Substrate heater

- Standard solvents for substrate cleaning (acetone, isopropanol, deionized water)

#### Procedure:

- Substrate Preparation:

- Clean the substrate ultrasonically in acetone, isopropanol, and deionized water for 15 minutes each.

- Dry the substrate with a stream of high-purity nitrogen gas.

- Mount the substrate onto the heater in the deposition chamber.

- Chamber Preparation:

- Place the target material onto the rotating target holder.

- $\circ$  Evacuate the chamber to a base pressure of at least  $10^{-6}$  Torr.

- Deposition:

- Heat the substrate to the desired deposition temperature (e.g., 200-400 °C for SnSe).

- Set the laser parameters: energy density (e.g., 1-3 J/cm²), repetition rate (e.g., 5-10 Hz).

- Ablate the target with the laser to deposit the film on the substrate. The deposition time will determine the final film thickness.

- Cooling and Characterization:

- After deposition, cool the substrate to room temperature in a high vacuum.

- Remove the sample from the chamber.

- Characterize the film using techniques such as X-ray Diffraction (XRD) for crystallinity,

Scanning Electron Microscopy (SEM) for morphology, and Atomic Force Microscopy

(AFM) for surface roughness.[9][10]

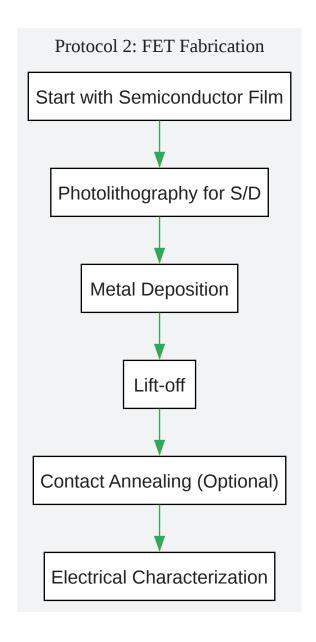

## **Protocol 2: Fabrication of a Field-Effect Transistor (FET)**

This protocol describes the fabrication of a bottom-gate, bottom-contact thin-film transistor, a common architecture for evaluating new semiconductor materials.[11]

Objective: To fabricate a field-effect transistor to characterize the electronic properties of a semiconductor thin film.

### Materials and Equipment:

- Substrate with pre-patterned gate and dielectric (e.g., heavily doped Si with a SiO<sub>2</sub> layer)

- Semiconductor thin film deposited via a suitable method (e.g., PLD as in Protocol 1)

- Photolithography equipment (photoresist, spinner, mask aligner, developer)

- Metal deposition system (e.g., thermal evaporator or sputter coater) for source/drain contacts (e.g., Au, Ti/Au)

- Lift-off chemicals (e.g., acetone)

- Semiconductor parameter analyzer

### Procedure:

- Substrate Preparation: Start with a clean, semiconductor-coated substrate (e.g., SnSe on Si/SiO<sub>2</sub>).

- Photolithography for Source-Drain Electrodes:

- Spin-coat a layer of photoresist onto the semiconductor film.

- Soft-bake the photoresist.

- Align a photomask defining the source and drain electrode patterns over the substrate.

- Expose the photoresist to UV light.

- Develop the photoresist to create the electrode pattern.

- Metal Deposition:

- Immediately transfer the substrate to a metal deposition system.

- Deposit the desired source-drain contact metals (e.g., a thin adhesion layer of Ti followed by Au).

- Lift-off:

- Immerse the substrate in acetone to dissolve the remaining photoresist, lifting off the excess metal and leaving the patterned electrodes.

- Rinse with isopropanol and dry with nitrogen.

- Annealing (Optional): Anneal the device in a controlled atmosphere (e.g., vacuum or inert gas) to improve the contact between the metal electrodes and the semiconductor.

- Characterization:

- Use a semiconductor parameter analyzer to measure the output and transfer characteristics of the FET.

- Key performance metrics to extract include field-effect mobility, on/off current ratio, and subthreshold swing.[12]

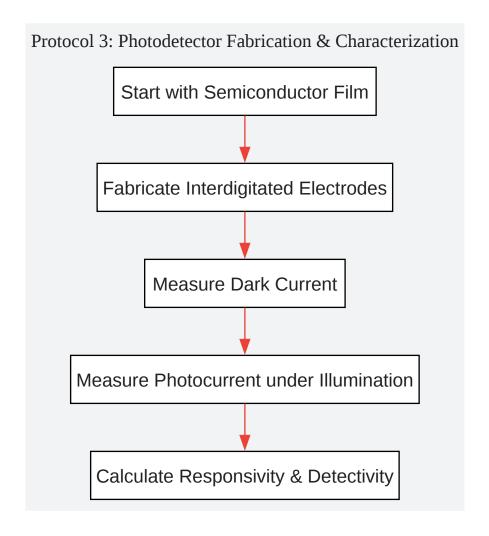

# Protocol 3: Fabrication of a Metal-Semiconductor-Metal (MSM) Photodetector

This protocol outlines the steps to create a simple planar photodetector to assess the photoresponsive properties of a material.[13]

Objective: To fabricate and characterize an MSM photodetector.

Materials and Equipment:

- Substrate with semiconductor thin film

- Photolithography equipment

- Metal deposition system (for interdigitated electrodes)

- Light source with variable wavelength and intensity (e.g., monochromator with a lamp source)

- Optical power meter

- Source meter for current-voltage measurements

### Procedure:

• Substrate and Semiconductor Deposition: Prepare the semiconductor thin film on an insulating substrate (e.g., quartz or glass).

### Electrode Patterning:

Use photolithography and metal deposition, similar to Protocol 2, to define a pattern of interdigitated electrodes on the semiconductor surface. This geometry maximizes the active area for photodetection.

#### Device Characterization:

- Place the device in a light-tight probe station.

- Measure the dark current by applying a bias voltage across the electrodes without illumination.

- Illuminate the device with a known optical power at a specific wavelength.

- Measure the photocurrent at the same bias voltage.

- Repeat for a range of wavelengths and optical powers.

- Performance Metrics Calculation:

- Responsivity (R): Calculate as R = (I\_photo I\_dark) / P\_in, where I\_photo is the

photocurrent, I\_dark is the dark current, and P\_in is the incident optical power.[14][15]

- Detectivity (D\*): A measure of the smallest detectable signal, calculated considering the noise sources, primarily the shot noise from the dark current.[14][15]

## **Visualized Experimental Workflows**

The following diagrams, generated using Graphviz, illustrate the logical flow of the experimental protocols described above.

Click to download full resolution via product page

Workflow for thin film synthesis via Pulsed Laser Deposition.

Click to download full resolution via product page

Fabrication workflow for a thin-film transistor.

Click to download full resolution via product page

Workflow for photodetector fabrication and characterization.

## **Challenges and Future Outlook**

The exploration of **tin arsenide** for semiconductor applications is in its infancy. Key challenges that need to be addressed include:

Phase Control: Developing synthesis methods that can selectively produce a specific stoichiometry and crystal structure of tin arsenide is paramount. The existence of metallic phases like Sn4As3 necessitates precise control during synthesis to isolate potentially semiconducting phases.[1]

- Material Characterization: A fundamental understanding of the electronic and optical properties of semiconducting SnAs phases is required. This includes accurate measurements of the band gap and carrier mobility, which are currently not welldocumented.

- Device Integration: Once a reliable synthesis for a semiconducting tin arsenide is

developed, significant work will be needed to integrate it into device architectures. This

includes developing appropriate dielectric interfaces, making low-resistance ohmic contacts,

and ensuring material stability during fabrication and operation.

Despite these challenges, the broader family of tin-based semiconductors continues to show promise for various applications in electronics and optoelectronics.[6][16] Future research into **tin arsenide** could uncover novel properties that make it a candidate for specialized applications. The protocols and data provided in these notes for analogous materials offer a solid foundation for such exploratory research.

### **Need Custom Synthesis?**

BenchChem offers custom synthesis for rare earth carbides and specific isotopiclabeling.

Email: info@benchchem.com or Request Quote Online.

### References

- 1. asu.elsevierpure.com [asu.elsevierpure.com]

- 2. mdpi.com [mdpi.com]

- 3. frontiersin.org [frontiersin.org]

- 4. mdpi.com [mdpi.com]

- 5. openaccesspub.org [openaccesspub.org]

- 6. researchgate.net [researchgate.net]

- 7. Arsenic-Doped SnSe Thin Films Prepared by Pulsed Laser Deposition PMC [pmc.ncbi.nlm.nih.gov]

- 8. pubs.acs.org [pubs.acs.org]

- 9. researchgate.net [researchgate.net]

- 10. Colloidal semiconductor nanocrystals: controlled synthesis and surface chemistry in organic media - RSC Advances (RSC Publishing) [pubs.rsc.org]

- 11. High-Performance Tin Oxide Thin-Film Transistors Realized by Codoping and Their Application in Logic Circuits: Abstract, Citation (BibTeX) & Reference | Bohrium [bohrium.com]

- 12. sst.semiconductor-digest.com [sst.semiconductor-digest.com]

- 13. Epitaxy Wikipedia [en.wikipedia.org]

- 14. Transformation: nanotechnology—challenges in transistor design and future technologies | springerprofessional.de [springerprofessional.de]

- 15. m.youtube.com [m.youtube.com]

- 16. mdpi.com [mdpi.com]

- To cite this document: BenchChem. [Application Notes and Protocols for Tin-Based Semiconductors in Device Fabrication]. BenchChem, [2025]. [Online PDF]. Available at: [https://www.benchchem.com/product/b12084615#using-tin-arsenide-in-semiconductor-devices]

### **Disclaimer & Data Validity:**

The information provided in this document is for Research Use Only (RUO) and is strictly not intended for diagnostic or therapeutic procedures. While BenchChem strives to provide accurate protocols, we make no warranties, express or implied, regarding the fitness of this product for every specific experimental setup.

**Technical Support:**The protocols provided are for reference purposes. Unsure if this reagent suits your experiment? [Contact our Ph.D. Support Team for a compatibility check]

Need Industrial/Bulk Grade? Request Custom Synthesis Quote

## BenchChem

Our mission is to be the trusted global source of essential and advanced chemicals, empowering scientists and researchers to drive progress in science and industry. Contact

Address: 3281 E Guasti Rd

Ontario, CA 91761, United States

Phone: (601) 213-4426

Email: info@benchchem.com