# Application Notes and Protocols for TIPS-TAP in Printed Electronics

Author: BenchChem Technical Support Team. Date: December 2025

For Researchers, Scientists, and Drug Development Professionals

This document provides detailed application notes and experimental protocols for the use of 6,13-bis(triisopropylsilylethynyl) pentacene (**TIPS-TAP** or commonly, TIPS-pentacene), a solution-processable small-molecule organic semiconductor, in the field of printed electronics.

## Introduction to TIPS-TAP in Printed Electronics

TIPS-pentacene is a p-type organic semiconductor that has garnered significant attention for its applications in printed electronics due to its excellent solution processability, high charge carrier mobility, and good ambient stability.[1] These properties make it an ideal candidate for fabricating low-cost, large-area, and flexible electronic devices such as Organic Field-Effect Transistors (OFETs), sensors, and integrated circuits using various printing techniques.

The addition of triisopropylsilylethynyl functional groups to the pentacene core enhances its solubility in common organic solvents, allowing for the formation of highly crystalline thin films through solution-based deposition methods.[1] The molecular packing of TIPS-pentacene in these films is crucial for achieving high device performance, and various printing techniques have been developed to control its crystallization and morphology.

# **Key Applications and Performance Data**

**TIPS-TAP** has been successfully employed in a range of printed electronic devices. The performance of these devices is highly dependent on the chosen deposition method, solvent

system, and processing conditions.

# **Organic Field-Effect Transistors (OFETs)**

OFETs are fundamental building blocks for various electronic circuits. TIPS-pentacene based OFETs have demonstrated impressive performance, making them suitable for applications in flexible displays, RFID tags, and sensors.

Table 1: Performance of Printed TIPS-Pentacene OFETs

| Printing<br>Technique | Substrate | Dielectric                      | Mobility<br>(cm²/Vs) | On/Off<br>Ratio   | Reference |

|-----------------------|-----------|---------------------------------|----------------------|-------------------|-----------|

| Solution<br>Shearing  | Si/SiO2   | OTS-treated<br>SiO <sub>2</sub> | up to 4.6            | > 10 <sup>6</sup> | [2]       |

| Inkjet Printing       | Glass     | PVP                             | 0.53                 | > 105             | [3]       |

| Drop Casting          | Si/SiO2   | OTS-treated<br>SiO <sub>2</sub> | ~0.1 - 1.0           | > 10 <sup>5</sup> | [1]       |

| Bar Coating           | Si/SiO2   | Polystyrene<br>(PS) blend       | up to 1.215          | > 10 <sup>6</sup> | [4]       |

# **Chemical Sensors**

The high surface-to-volume ratio and sensitivity of the conductive channel to surface adsorbates make TIPS-pentacene OFETs excellent candidates for chemical sensing applications.

Table 2: Performance of a Printed TIPS-Pentacene Gas Sensor

| Analyte                   | Sensor<br>Type | Printing<br>Method | Sensitivity | Limit of<br>Detection<br>(LOD) | Reference |

|---------------------------|----------------|--------------------|-------------|--------------------------------|-----------|

| Nitrogen<br>Dioxide (NO2) | Chemiresistor  | Drop Casting       | > 1000%/ppm | 20 ppb                         | [5]       |

# **Experimental Protocols**

The following are detailed protocols for the fabrication and characterization of TIPS-pentacene based printed electronic devices.

## **Protocol 1: Fabrication of OFETs by Solution Shearing**

Solution shearing is a technique that allows for the deposition of highly crystalline and aligned organic semiconductor films, leading to high-performance devices.[2]

## Materials and Equipment:

- TIPS-pentacene powder

- · Toluene, HPLC grade

- Substrates (e.g., heavily n-doped Si wafers with a 200 nm thermal oxide layer)

- Octadecyltrichlorosilane (OTS) for surface treatment

- Solution shearing setup with a heated stage and a shearing blade (e.g., an OTS-treated Si wafer)

- Hot plate, spin coater, vacuum oven

## Procedure:

- Substrate Preparation:

- Clean the Si/SiO<sub>2</sub> substrates by sonicating in acetone and isopropyl alcohol for 15 minutes each, then dry with a nitrogen stream.

- Treat the substrates with an oxygen plasma or a piranha solution to create a hydrophilic surface.

- Apply an OTS self-assembled monolayer (SAM) by vapor deposition or solution immersion to create a hydrophobic surface, which promotes the desired crystal growth of TIPSpentacene.

- TIPS-Pentacene Solution Preparation:

- Prepare a solution of TIPS-pentacene in toluene at a concentration of 8 mg/mL.

- Heat the solution at 60°C with stirring for 45 minutes to ensure complete dissolution.

- Just before deposition, increase the solution temperature to 90°C.

- Solution Shearing Deposition:

- Place the prepared substrate on the heated stage of the solution shearing setup, set to 90°C.

- $\circ\,$  Position the shearing blade at a small angle and a defined gap (e.g., 100  $\mu m)$  above the substrate.

- Dispense a small volume of the hot TIPS-pentacene solution into the gap between the blade and the substrate.

- Move the substrate at a constant speed (e.g., 0.8 4 mm/s) relative to the stationary blade. The shearing speed influences the crystal packing and resulting mobility.

- Allow the solvent to evaporate, leaving a crystalline TIPS-pentacene film.

- Electrode Deposition:

- Deposit source and drain electrodes (e.g., 50 nm of gold) on top of the TIPS-pentacene film through a shadow mask using thermal evaporation. This creates a top-contact, bottom-gate OFET structure.

## Protocol 2: Fabrication of OFETs by Inkjet Printing

Inkjet printing offers digital control over the deposition process, enabling the fabrication of complex patterns and circuits with high material efficiency.[3]

Materials and Equipment:

TIPS-pentacene powder

- Anisole and chlorobenzene (or other suitable high-boiling-point solvents)

- Poly(4-vinylphenol) (PVP) for the dielectric layer

- Cross-linking agent (e.g., poly(melamine-co-formaldehyde))

- Substrates (e.g., glass or flexible PET)

- Inkjet printer with piezoelectric printheads (e.g., Dimatix)

- Silver nanoparticle ink for electrodes

- · UV curing system, oven

## Procedure:

- Substrate and Dielectric Layer Preparation:

- Clean the substrate thoroughly.

- If using a glass substrate, a gate electrode (e.g., patterned ITO) may be pre-deposited.

- Prepare a solution of PVP and a cross-linking agent in a suitable solvent (e.g., PGMEA).

- Spin-coat or inkjet-print the PVP solution onto the substrate to form the gate dielectric layer.

- Cross-link the PVP layer by baking at an elevated temperature (e.g., 175°C).

- Ink Formulation:

- Prepare an ink by dissolving TIPS-pentacene in a high-boiling-point solvent such as anisole or a mixture of solvents to achieve the desired viscosity and surface tension for stable jetting. A typical concentration is 1-5 mg/mL.

- The ink may also contain a polymer binder (e.g., polystyrene or polycarbonate) to improve film morphology.[3]

- Inkjet Printing of Electrodes and Semiconductor:

- Print the source and drain electrodes using a silver nanoparticle ink. Sinter the printed silver at a temperature compatible with the substrate.

- Inkjet-print the TIPS-pentacene ink onto the channel region between the source and drain electrodes.

- Control the substrate temperature during printing to influence solvent evaporation and crystal growth.

- Post-Deposition Annealing:

- Anneal the printed device at a moderate temperature (e.g., 60-80°C) to improve the crystallinity of the TIPS-pentacene film and the conductivity of the electrodes.

## **Protocol 3: Characterization of Printed OFETs**

## Equipment:

- Semiconductor parameter analyzer or source-measure units

- Probe station

## Procedure:

- Transfer Characteristics:

- Connect the source, drain, and gate terminals of the OFET to the parameter analyzer.

- Apply a constant drain-source voltage (Vds), typically in the saturation regime (e.g., -40

V).

- Sweep the gate-source voltage (Vgs) from positive to negative values (e.g., +20 V to -40 V).

- Measure the drain current (Id).

- Plot Id vs. Vgs. The on/off ratio is the ratio of the maximum to the minimum Id.

- Output Characteristics:

- Apply a constant Vgs.

- Sweep Vds from 0 V to a negative value (e.g., -40 V).

- Measure Id.

- Repeat for several values of Vgs.

- Plot Id vs. Vds.

- Mobility Calculation:

- From the transfer curve in the saturation regime, the field-effect mobility ( $\mu$ ) can be calculated using the following equation:  $I_d = (W/2L) * C_i * \mu * (V_gs V_th)^2$

- Where:

- I\_d is the drain current

- W is the channel width

- L is the channel length

- C i is the capacitance per unit area of the gate dielectric

- V\_gs is the gate-source voltage

- V\_th is the threshold voltage

## **Visualizations**

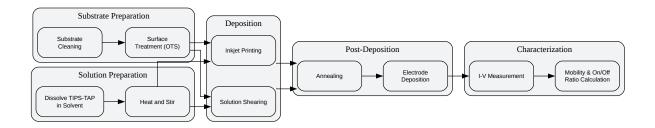

# **Experimental Workflows**

The following diagrams illustrate the key experimental workflows for fabricating and characterizing **TIPS-TAP** based printed electronic devices.

Click to download full resolution via product page

Caption: Workflow for OFET fabrication and characterization.

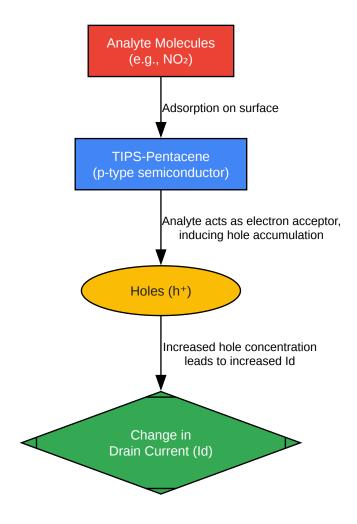

# Signaling Pathway for a Chem-FET Sensor

This diagram illustrates the principle of a chemiresistive field-effect transistor (Chem-FET) sensor based on TIPS-pentacene.

Click to download full resolution via product page

Caption: Sensing mechanism of a p-type TIPS-pentacene Chem-FET.

## **Need Custom Synthesis?**

BenchChem offers custom synthesis for rare earth carbides and specific isotopiclabeling.

Email: info@benchchem.com or Request Quote Online.

# References

- 1. ossila.com [ossila.com]

- 2. pubs.aip.org [pubs.aip.org]

- 3. [PDF] Inkjet-printed organic thin film transistors based on TIPS pentacene with insulating polymers | Semantic Scholar [semanticscholar.org]

- 4. Engineered molecular stacking crystallinity of bar-coated TIPS-pentacene/polystyrene films for organic thin-film transistors PMC [pmc.ncbi.nlm.nih.gov]

- 5. researchgate.net [researchgate.net]

- To cite this document: BenchChem. [Application Notes and Protocols for TIPS-TAP in Printed Electronics]. BenchChem, [2025]. [Online PDF]. Available at: [https://www.benchchem.com/product/b14037076#tips-tap-applications-in-printed-electronics]

## **Disclaimer & Data Validity:**

The information provided in this document is for Research Use Only (RUO) and is strictly not intended for diagnostic or therapeutic procedures. While BenchChem strives to provide accurate protocols, we make no warranties, express or implied, regarding the fitness of this product for every specific experimental setup.

**Technical Support:**The protocols provided are for reference purposes. Unsure if this reagent suits your experiment? [Contact our Ph.D. Support Team for a compatibility check]

Need Industrial/Bulk Grade? Request Custom Synthesis Quote

# BenchChem

Our mission is to be the trusted global source of essential and advanced chemicals, empowering scientists and researchers to drive progress in science and industry. Contact

Address: 3281 E Guasti Rd

Ontario, CA 91761, United States

Phone: (601) 213-4426

Email: info@benchchem.com