# Application Notes and Protocols for PBI-based Organic Thin-Film Transistors

Author: BenchChem Technical Support Team. Date: December 2025

| Compound of Interest |          |           |

|----------------------|----------|-----------|

| Compound Name:       | PBI 51   |           |

| Cat. No.:            | B1678569 | Get Quote |

Topic: Perylene Bisimide (PBI) Derivatives in Organic Thin-Film Transistor (OTFT) Fabrication

Audience: Researchers, scientists, and drug development professionals.

Note on Nomenclature: The term "**PBI 51**" does not correspond to a standard nomenclature for a specific Perylene Bisimide derivative. This document focuses on a well-characterized and high-performance PBI derivative, N,N'-bis(heptafluorobutyl)-3,4:9,10-perylene diimide (PTCDI-C4F7), as a representative example for the fabrication of n-channel organic thin-film transistors. The protocols and data presented herein are based on published research for this specific compound.

#### Introduction

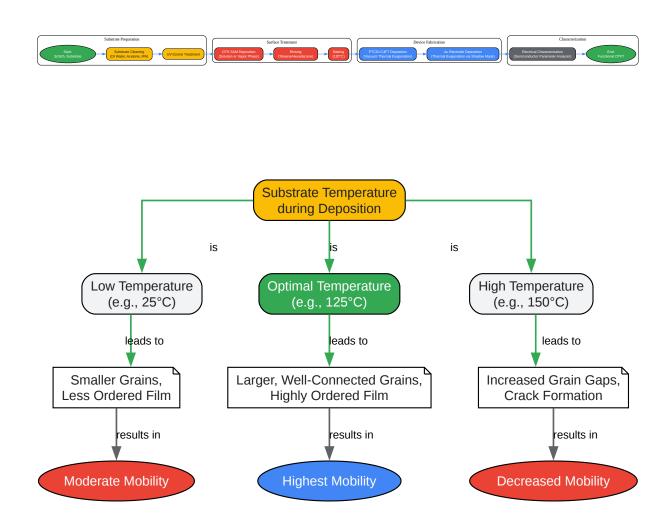

Perylene bisimide (PBI) derivatives are a class of n-type organic semiconductors known for their high electron affinity, excellent chemical and thermal stability, and strong light absorption. These properties make them promising candidates for a variety of organic electronic devices, including organic thin-film transistors (OTFTs). PTCDI-C4F7, in particular, has demonstrated high electron mobility and remarkable air stability, making it an attractive material for the fabrication of robust n-channel transistors. This application note provides a summary of the performance of PTCDI-C4F7 based OTFTs, a detailed protocol for their fabrication and characterization, and graphical representations of the experimental workflow and the influence of fabrication parameters on device performance.

#### **Data Presentation**

The performance of OTFTs is characterized by several key parameters, including the field-effect mobility ( $\mu$ ), the on/off current ratio (lon/loff), and the threshold voltage (Vth). The following table summarizes the electrical characteristics of OTFTs fabricated with PTCDI-C4F7 as the active semiconductor layer, under various deposition and measurement conditions.

| Substrate Temperature during Deposition (°C) | Measurement<br>Atmosphere | Electron<br>Mobility (µ)<br>(cm²/Vs) | On/Off Ratio<br>(lon/loff) | Threshold<br>Voltage (Vth)<br>(V) |

|----------------------------------------------|---------------------------|--------------------------------------|----------------------------|-----------------------------------|

| 25                                           | Nitrogen                  | ~0.63                                | > 105                      | ~35-45                            |

| 90                                           | Nitrogen                  | ~0.70                                | > 105                      | ~35-45                            |

| 125                                          | Nitrogen                  | ~0.72                                | > 105                      | ~35-45                            |

| 150                                          | Nitrogen                  | Lower mobility observed              | -                          | -                                 |

| 125                                          | Air                       | ~0.51 ± 0.05                         | ~105                       | Increased compared to N2          |

Data compiled from published research. The performance can vary based on specific experimental conditions.

## **Experimental Protocols**

This section details the procedures for the fabrication and characterization of top-contact, bottom-gate OTFTs using PTCDI-C4F7.

#### **Substrate Preparation and Dielectric Surface Treatment**

A heavily doped n-type silicon wafer with a thermally grown silicon dioxide (SiO<sub>2</sub>) layer (typically 200-300 nm thick) is commonly used as the substrate and gate dielectric, respectively. A crucial step for achieving high performance in n-type OTFTs is the surface treatment of the SiO<sub>2</sub> layer to passivate charge traps.

Protocol for Octadecyltrichlorosilane (OTS) Treatment:

- Substrate Cleaning:

- Ultrasonically clean the Si/SiO<sub>2</sub> substrates in a sequence of deionized water, acetone, and isopropanol for 15 minutes each.

- Dry the substrates with a stream of dry nitrogen.

- Treat the substrates with UV-ozone for 15-20 minutes to remove any remaining organic residues and to generate hydroxyl (-OH) groups on the SiO<sub>2</sub> surface, which are necessary for the silanization reaction.

- OTS Self-Assembled Monolayer (SAM) Formation:

- Prepare a solution of OTS in a non-polar solvent such as toluene or hexadecane (e.g., 5-10 mM concentration).

- Immerse the cleaned and dried substrates in the OTS solution for 12-48 hours at room temperature, or for a shorter duration at an elevated temperature (e.g., 100 °C for 1 hour in a vacuum oven for vapor phase deposition). The process should be carried out in a lowhumidity environment, such as a nitrogen-filled glovebox, to prevent uncontrolled polymerization of OTS in the solution.

- After immersion, rinse the substrates thoroughly with the pure solvent (toluene or hexadecane) to remove any physisorbed OTS molecules.

- Finally, bake the substrates at 120 °C for 10-15 minutes to promote the cross-linking of the OTS monolayer.

#### **Organic Semiconductor Deposition**

The active layer of PTCDI-C4F7 is deposited onto the OTS-treated SiO<sub>2</sub> surface via thermal evaporation in a high-vacuum chamber.

Protocol for Vacuum Deposition of PTCDI-C4F7:

Place the OTS-treated substrates into a high-vacuum chamber.

- Load high-purity PTCDI-C4F7 powder into a thermal evaporation source (e.g., a quartz crucible).

- Evacuate the chamber to a base pressure of less than 1 x 10-6 Torr.

- Heat the substrate holder to the desired temperature (e.g., 125 °C for optimal performance).

- Gradually heat the evaporation source until the PTCDI-C4F7 starts to sublimate.

- Deposit a thin film of PTCDI-C4F7 onto the substrates at a controlled deposition rate (typically 0.1-0.5 Å/s). The final thickness of the film is usually in the range of 40-60 nm, monitored in-situ using a quartz crystal microbalance.

- After deposition, allow the substrates to cool down to room temperature before venting the chamber.

#### **Electrode Deposition**

Top-contact source and drain electrodes are deposited onto the organic semiconductor layer through a shadow mask. Gold (Au) is a common choice for the electrode material due to its high work function and inertness.

Protocol for Gold Electrode Evaporation:

- Align a shadow mask with the desired channel dimensions (e.g., channel length of 50-100 µm and channel width of 1-2 mm) over the PTCDI-C4F7 coated substrates.

- Return the substrates to the high-vacuum chamber.

- Evaporate a thin layer of gold (typically 40-60 nm) through the shadow mask at a deposition rate of approximately 1.0 Å/s. A thin adhesion layer of chromium or titanium (2-5 nm) may be deposited prior to the gold.

- Remove the substrates from the chamber after the electrode deposition is complete.

#### **Electrical Characterization**

The electrical performance of the fabricated OTFTs is measured using a semiconductor parameter analyzer in a controlled environment (e.g., in a nitrogen-filled glovebox or in ambient air).

#### Procedure for OTFT Characterization:

- Contact the source, drain, and gate electrodes of the transistor using microprobes.

- Output Characteristics (Ids vs. Vds):

- Apply a gate voltage (Vgs) and sweep the drain-source voltage (Vds) from 0 V to a higher voltage (e.g., 80-100 V).

- Repeat this sweep for several different gate voltages (e.g., in steps of 10-20 V).

- Transfer Characteristics (Ids vs. Vgs):

- Apply a constant drain-source voltage (Vds) (e.g., 80-100 V).

- Sweep the gate voltage (Vgs) from a negative value (e.g., -20 V) to a positive value (e.g., 80-100 V) and measure the drain-source current (Ids).

- Parameter Extraction:

- $\circ$  The field-effect mobility ( $\mu$ ) is calculated from the slope of the (lds)1/2 vs. Vgs plot in the saturation regime.

- The on/off ratio (Ion/Ioff) is the ratio of the maximum to the minimum drain-source current in the transfer curve.

- The threshold voltage (Vth) is determined by extrapolating the linear portion of the (lds)1/2

vs. Vgs plot to zero current.

## Mandatory Visualizations Experimental Workflow

The following diagram illustrates the sequential steps involved in the fabrication of a top-contact, bottom-gate OTFT with PTCDI-C4F7.

Click to download full resolution via product page

To cite this document: BenchChem. [Application Notes and Protocols for PBI-based Organic Thin-Film Transistors]. BenchChem, [2025]. [Online PDF]. Available at: [https://www.benchchem.com/product/b1678569#pbi-51-in-organic-thin-film-transistor-fabrication]

#### **Disclaimer & Data Validity:**

The information provided in this document is for Research Use Only (RUO) and is strictly not intended for diagnostic or therapeutic procedures. While BenchChem strives to provide

accurate protocols, we make no warranties, express or implied, regarding the fitness of this product for every specific experimental setup.

**Technical Support:** The protocols provided are for reference purposes. Unsure if this reagent suits your experiment? [Contact our Ph.D. Support Team for a compatibility check]

Need Industrial/Bulk Grade? Request Custom Synthesis Quote

## BenchChem

Our mission is to be the trusted global source of essential and advanced chemicals, empowering scientists and researchers to drive progress in science and industry. Contact

Address: 3281 E Guasti Rd

Ontario, CA 91761, United States

Phone: (601) 213-4426

Email: info@benchchem.com