## Application Notes and Protocols for Interface Engineering in α-Sexithiophene Organic Electronic Devices

Author: BenchChem Technical Support Team. Date: December 2025

| Compound of Interest |                     |           |  |  |  |  |

|----------------------|---------------------|-----------|--|--|--|--|

| Compound Name:       | alpha-Sexithiophene |           |  |  |  |  |

| Cat. No.:            | B1246321            | Get Quote |  |  |  |  |

For Researchers, Scientists, and Drug Development Professionals

These application notes provide a comprehensive overview and detailed protocols for interface engineering in **alpha-sexithiophene** ( $\alpha$ -6T) based organic electronic devices. The strategic modification of semiconductor-dielectric and semiconductor-electrode interfaces is crucial for optimizing device performance, including charge carrier mobility, threshold voltage, and contact resistance. This document outlines key experimental procedures, presents comparative data, and visualizes critical workflows and concepts.

# Introduction to Interface Engineering in $\alpha$ -Sexithiophene Devices

**Alpha-sexithiophene** ( $\alpha$ -6T) is a well-studied p-type organic semiconductor used in organic field-effect transistors (OFETs) and organic light-emitting diodes (OLEDs). The performance of these devices is highly sensitive to the interfaces between the  $\alpha$ -6T active layer and the dielectric and electrode materials.[1][2][3] Charge transport in OFETs occurs within the first few molecular layers of the semiconductor at the dielectric interface.[1][4] Therefore, controlling the molecular ordering, morphology, and electronic properties at this interface is paramount for achieving high device performance.[1][5][6]

Interface engineering strategies for  $\alpha$ -6T devices primarily focus on two key areas:

- The Semiconductor/Dielectric Interface: Modifications to the gate dielectric surface can influence the growth mode and molecular orientation of the α-6T film, which in turn affects charge transport properties.[1][4][6]

- The Semiconductor/Electrode Interface: Tailoring the work function of the source and drain electrodes can reduce the charge injection barrier, leading to lower contact resistance and improved device performance.[7][8]

Self-assembled monolayers (SAMs) are a powerful and widely used tool for interface engineering, allowing for precise control over surface energy and electronic properties.[9][10] [11][12][13]

## **Quantitative Data Summary**

The following tables summarize key performance metrics of  $\alpha$ -6T based organic field-effect transistors (OFETs) with various interface modifications.

Table 1: Influence of Dielectric Surface Modification on α-6T OFET Performance

| Dielectric<br>System | α-6T<br>Deposition<br>Temperatur<br>e (°C) | Field-Effect<br>Mobility<br>(cm²/Vs) | On/Off<br>Ratio   | Threshold<br>Voltage (V) | Reference |

|----------------------|--------------------------------------------|--------------------------------------|-------------------|--------------------------|-----------|

| SiO <sub>2</sub>     | 120                                        | ~0.03                                | > 10 <sup>5</sup> | -                        | [4]       |

| SiO <sub>2</sub>     | 100                                        | 0.24                                 | -                 | -                        | [14]      |

| Rubbed<br>Polymer    | Room<br>Temperature                        | Enhanced<br>anisotropy               | -                 | -                        | [1]       |

Table 2: Impact of Electrode Modification on  $\alpha$ -6T Derivative OFETs

| Semiconducto<br>r | Electrode<br>Modification               | Contact<br>Resistance<br>(kΩ·cm)                  | Field-Effect<br>Mobility<br>(cm²/Vs) | Reference |

|-------------------|-----------------------------------------|---------------------------------------------------|--------------------------------------|-----------|

| DH7T              | Untreated Au                            | -                                                 | 0.12                                 | [7]       |

| DH5T              | Untreated Au                            | Non-zero<br>(causes bending<br>in transfer curve) | -                                    | [7]       |

| Pentacene         | Alkanethiol SAM<br>on Au                | Decreased                                         | -                                    | [8]       |

| Pentacene         | Fluorinated<br>Alkanethiol SAM<br>on Au | Increased                                         | -                                    | [8]       |

Note: DHnT refers to  $\alpha$ , $\omega$ -dihexyl-oligothiophenes where n is the number of thiophene units.

### **Experimental Protocols**

This section provides detailed methodologies for key experiments in the fabrication and characterization of  $\alpha$ -6T devices with engineered interfaces.

### **Protocol for Substrate and Dielectric Preparation**

A common substrate for  $\alpha$ -6T OFETs is a highly doped silicon wafer (acting as the gate electrode) with a thermally grown silicon dioxide (SiO<sub>2</sub>) layer (acting as the gate dielectric).

- Substrate Cleaning:

- 1. Sequentially sonicate the Si/SiO<sub>2</sub> substrates in deionized water, acetone, and isopropanol for 15 minutes each.[15]

- 2. Dry the substrates with a stream of high-purity nitrogen gas.

- 3. Treat the substrates with an oxygen plasma or UV-ozone cleaner for 5-10 minutes to remove any remaining organic residues and to create a hydrophilic surface.[15]

- Dielectric Surface Modification with Self-Assembled Monolayers (e.g., Hexamethyldisilazane

HMDS):

- 1. Place the cleaned substrates in a vacuum desiccator along with a small open vial containing a few drops of HMDS.

- 2. Evacuate the desiccator to create a vapor-phase environment.

- 3. Allow the vapor-phase silanization to proceed for at least 12 hours at room temperature. This process renders the SiO<sub>2</sub> surface hydrophobic.

- 4. Alternatively, for solution-phase deposition of other silanes like octadecyltrichlorosilane (OTS), immerse the cleaned and activated substrates in a dilute solution (e.g., 1-10 mM) of the silane in an anhydrous solvent (e.g., toluene or hexane) for a specified time (30 minutes to 24 hours), followed by rinsing with the pure solvent and curing at elevated temperature (e.g., 120 °C).

# Protocol for Electrode Modification with Thiol-Based SAMs

This protocol is for modifying gold (Au) source and drain electrodes in a bottom-contact, bottom-gate device architecture.

- Substrate Preparation: Use a pre-patterned substrate with Au electrodes or fabricate electrodes using standard photolithography and lift-off processes.[16]

- Cleaning: Clean the substrate with the Au electrodes as described in Protocol 3.1.1. The final

O<sub>2</sub> plasma or UV-ozone step is critical for activating the gold surface.[15]

- SAM Formation:

- 1. Prepare a dilute solution (e.g., 1-5 mM) of the desired thiol (e.g., octadecanethiol or a fluorinated alkanethiol) in a high-purity solvent like ethanol or isopropanol.

- 2. Immediately after cleaning, immerse the substrate in the thiol solution.[15]

- 3. Allow the SAM to self-assemble on the gold surfaces by leaving the substrate in the solution for 30 minutes to 24 hours at room temperature.[15]

- 4. After immersion, thoroughly rinse the substrate with the pure solvent to remove any physisorbed molecules.

- 5. Dry the substrate with a stream of nitrogen gas.

#### **Protocol for Vacuum Deposition of α-Sexithiophene**

Thermal evaporation under high vacuum is a standard method for depositing high-purity thin films of  $\alpha$ -6T.[17]

- System Preparation:

- 1. Load the prepared substrates into a high-vacuum deposition chamber (base pressure  $< 10^{-6}$  Torr).

- 2. Place high-purity  $\alpha$ -6T powder (purified by gradient sublimation) into a thermal evaporation source (e.g., a resistively heated boat made of tungsten or molybdenum).

- Deposition Parameters:

- 1. Heat the substrate to the desired temperature (e.g., room temperature, 100 °C, or 120 °C) to control the film morphology.[14][18]

- 2. Gradually heat the evaporation source until the  $\alpha$ -6T starts to sublimate.

- 3. Monitor the deposition rate and film thickness using a quartz crystal microbalance. A typical deposition rate is 0.1-0.5 Å/s.[4]

- 4. Deposit a film of the desired thickness, typically 20-50 nm for OFET applications.

- Post-Deposition:

- 1. Allow the system to cool down before venting to atmospheric pressure to prevent thermal shock and film contamination.

2. For top-contact devices, subsequently deposit the source and drain electrodes (e.g., Au) through a shadow mask.

#### **Visualizations**

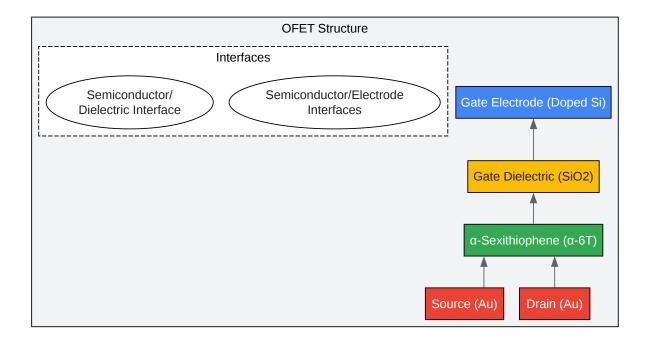

The following diagrams illustrate key structures, workflows, and physical principles involved in the interface engineering of  $\alpha$ -6T devices.

Click to download full resolution via product page

Caption: Key interfaces in a bottom-gate, bottom-contact  $\alpha$ -6T OFET.

#### Click to download full resolution via product page

Caption: Workflow for fabricating an  $\alpha$ -6T OFET with interface modification.

Caption: Energy level alignment at the  $Au/\alpha$ -6T interface with and without a SAM.

#### **Need Custom Synthesis?**

BenchChem offers custom synthesis for rare earth carbides and specific isotopiclabeling.

Email: info@benchchem.com or Request Quote Online.

#### References

- 1. crg.postech.ac.kr [crg.postech.ac.kr]

- 2. Engineering of the dielectric—semiconductor interface in organic field-effect transistors Journal of Materials Chemistry (RSC Publishing) [pubs.rsc.org]

- 3. app.cafeprozhe.com [app.cafeprozhe.com]

- 4. researchgate.net [researchgate.net]

- 5. Enhanced mobility in organic field-effect transistors due to semiconductor/dielectric iInterface control and very thin single crystal PubMed [pubmed.ncbi.nlm.nih.gov]

- 6. researchgate.net [researchgate.net]

- 7. pubs.aip.org [pubs.aip.org]

- 8. researchwithnj.com [researchwithnj.com]

- 9. Studies of the Interfaces between Conjugated Oligomers and Self-Assembled Monolayers [acswebcontent.acs.org]

- 10. Interface Engineering with Self-assembled Monolayers for Organic Electronics [library.oapen.org]

- 11. researchgate.net [researchgate.net]

- 12. Recent progress in interface engineering of organic thin film transistors with self-assembled monolayers Materials Chemistry Frontiers (RSC Publishing) [pubs.rsc.org]

- 13. ias.ac.in [ias.ac.in]

- 14. researchgate.net [researchgate.net]

- 15. benchchem.com [benchchem.com]

- 16. researchgate.net [researchgate.net]

- 17. www-solar.materials.ox.ac.uk [www-solar.materials.ox.ac.uk]

- 18. pubs.acs.org [pubs.acs.org]

- To cite this document: BenchChem. [Application Notes and Protocols for Interface Engineering in α-Sexithiophene Organic Electronic Devices]. BenchChem, [2025]. [Online PDF]. Available at: [https://www.benchchem.com/product/b1246321#interface-engineering-in-alpha-sexithiophene-organic-electronic-devices]

#### **Disclaimer & Data Validity:**

The information provided in this document is for Research Use Only (RUO) and is strictly not intended for diagnostic or therapeutic procedures. While BenchChem strives to provide accurate protocols, we make no warranties, express or implied, regarding the fitness of this product for every specific experimental setup.

**Technical Support:**The protocols provided are for reference purposes. Unsure if this reagent suits your experiment? [Contact our Ph.D. Support Team for a compatibility check]

Need Industrial/Bulk Grade? Request Custom Synthesis Quote

## BenchChem

Our mission is to be the trusted global source of essential and advanced chemicals, empowering scientists and researchers to drive progress in science and industry. Contact

Address: 3281 E Guasti Rd

Ontario, CA 91761, United States

Phone: (601) 213-4426

Email: info@benchchem.com