# Application Notes and Protocols for Fabricating SnSe<sub>2</sub>-Based Field-Effect Transistors

Author: BenchChem Technical Support Team. Date: December 2025

For Researchers, Scientists, and Drug Development Professionals

This document provides a comprehensive guide for the fabrication and characterization of tin diselenide (SnSe<sub>2</sub>)-based field-effect transistors (FETs). SnSe<sub>2</sub>, a layered two-dimensional (2D) material, has garnered significant interest for its potential in next-generation electronic and optoelectronic devices. These protocols and application notes are designed to furnish researchers with the necessary details to successfully fabricate and evaluate SnSe<sub>2</sub> FETs in a laboratory setting.

# Performance of SnSe<sub>2</sub>-Based Field-Effect Transistors

The performance of SnSe<sub>2</sub> FETs is influenced by several factors, including the thickness of the SnSe<sub>2</sub> flake, the type of gate dielectric used, and the choice of electrode materials. A summary of key performance metrics from various studies is presented in the table below to facilitate comparison.

| SnSe <sub>2</sub> Thicknes s | Gate<br>Dielectric                              | Electrode<br>Material | Mobility<br>(cm²/Vs) | On/Off<br>Ratio               | Gate<br>Configura<br>tion | Referenc<br>e |

|------------------------------|-------------------------------------------------|-----------------------|----------------------|-------------------------------|---------------------------|---------------|

| 3.7 nm                       | 70 nm HfO <sub>2</sub> with polymer electrolyte | Not<br>Specified      | -                    | > 104                         | Back-gated                | [1]           |

| 5 nm                         | DI water                                        | Not<br>Specified      | 440                  | 105                           | Top-gated                 | [2]           |

| 6.6 nm                       | 300 nm<br>SiO <sub>2</sub>                      | Ti/Au (5/50<br>nm)    | -                    | ~10 <sup>5</sup> (at 78<br>K) | Back-gated                | [3]           |

| 8.6 nm                       | 300 nm<br>SiO <sub>2</sub>                      | Ti/Au (5/50<br>nm)    | 85 (at 300<br>K)     | Not<br>specified              | Back-gated                | [3][4]        |

| 21 nm                        | Not<br>Specified                                | Not<br>Specified      | 26.6                 | Not<br>Specified              | Not<br>Specified          | [5]           |

| 300 nm                       | Not<br>Specified                                | Not<br>Specified      | 3.76                 | Not<br>Specified              | Not<br>Specified          | [5]           |

| Few-layer                    | 300 nm<br>SiO <sub>2</sub>                      | Not<br>Specified      | 41                   | ~1                            | Back-gated                | [1]           |

| Few-layer                    | 70 nm<br>HfO <sub>2</sub>                       | Not<br>Specified      | -                    | > 101                         | Back-gated                | [1]           |

| Few-layer                    | DI water                                        | Ti/Au                 | ~127                 | ~104                          | Top-gated                 | [6]           |

## **Experimental Protocols**

This section details the step-by-step procedures for the fabrication of SnSe<sub>2</sub>-based FETs, from substrate preparation to device characterization.

## Substrate Preparation (SiO<sub>2</sub>/Si)

A clean substrate is crucial for the successful fabrication of high-quality devices.

- Sonication: Place the SiO<sub>2</sub>/Si substrates in a beaker with acetone and sonicate for 15 minutes.

- Second Sonication: Transfer the substrates to a beaker with isopropyl alcohol (IPA) and sonicate for another 15 minutes.

- Drying: Dry the substrates using a stream of dry nitrogen (N2).

- Oxygen Plasma Treatment (Optional but Recommended): Place the substrates in an oxygen plasma asher for 3-5 minutes to remove any remaining organic residues and to enhance the hydrophilicity of the surface, which can improve the adhesion of the SnSe<sub>2</sub> flakes.

#### Mechanical Exfoliation of SnSe<sub>2</sub> Flakes

This protocol describes the "Scotch tape" method for obtaining thin SnSe<sub>2</sub> flakes from a bulk crystal.

- Tape Preparation: Take a piece of high-quality dicing or Scotch tape.

- Crystal Cleavage: Press the adhesive side of the tape firmly against a bulk SnSe2 crystal.

- Repeated Peeling: Peel the tape off the crystal. You will observe that a thin layer of SnSe<sub>2</sub> adheres to the tape. Fold the tape onto itself and peel it apart multiple times. This repeated cleaving process will result in progressively thinner layers of SnSe<sub>2</sub> on the tape.

- Transfer to Substrate: Gently press the tape with the exfoliated SnSe<sub>2</sub> flakes onto the cleaned SiO<sub>2</sub>/Si substrate.

- Tape Removal: Slowly peel the tape off the substrate. Thin SnSe<sub>2</sub> flakes of varying thicknesses will be left on the substrate.

- Flake Identification: Use an optical microscope to identify suitable thin flakes. Monolayer and few-layer flakes are often nearly transparent with faint contrast. Atomic Force Microscopy (AFM) can be used for precise thickness determination.

# Transfer of SnSe<sub>2</sub> Flakes using Polydimethylsiloxane (PDMS)

For more precise placement of exfoliated flakes, a PDMS stamp transfer method can be employed.

- PDMS Stamp Preparation: Prepare a PDMS stamp by mixing the PDMS precursor and curing agent (typically in a 10:1 ratio), degassing the mixture in a vacuum chamber, and curing it in an oven.

- Exfoliation onto PDMS: Exfoliate SnSe<sub>2</sub> flakes onto the surface of the PDMS stamp using the "Scotch tape" method described above.

- Flake Selection: Identify a suitable thin flake on the PDMS stamp using an optical microscope.

- Alignment and Transfer: Using a micromanipulator, align the selected SnSe<sub>2</sub> flake on the PDMS stamp with the desired location on the target SiO<sub>2</sub>/Si substrate.

- Contact and Release: Bring the PDMS stamp into contact with the substrate. Slowly retract the PDMS stamp, leaving the SnSe<sub>2</sub> flake on the substrate. The transfer is facilitated by the difference in adhesion energy between SnSe<sub>2</sub>/PDMS and SnSe<sub>2</sub>/SiO<sub>2</sub>.

## **Device Fabrication: Patterning of Electrodes**

Source and drain electrodes are patterned using either photolithography or electron-beam lithography (EBL). EBL offers higher resolution for smaller device features.

#### A. Photolithography

- Resist Coating: Spin-coat a layer of photoresist (e.g., S1813) onto the substrate with the transferred SnSe<sub>2</sub> flake.

- Soft Bake: Bake the substrate on a hotplate at the temperature and for the duration specified by the photoresist manufacturer (e.g., 115°C for 60 seconds).

- Alignment and Exposure: Align a photomask with the desired electrode pattern over the substrate. Expose the photoresist to UV light through the photomask.

- Development: Immerse the substrate in a developer solution (e.g., MF-319) to remove the exposed photoresist (for a positive resist).

- Metal Deposition: Deposit the desired electrode metals (e.g., a 5 nm Ti adhesion layer followed by 50 nm of Au) using an electron-beam evaporator or thermal evaporator.

- Lift-off: Immerse the substrate in a solvent (e.g., acetone) to dissolve the remaining photoresist, lifting off the excess metal and leaving the patterned electrodes in contact with the SnSe<sub>2</sub> flake.

- B. Electron-Beam Lithography (EBL)

- Resist Coating: Spin-coat a layer of EBL resist (e.g., PMMA) onto the substrate.

- Soft Bake: Bake the substrate according to the resist manufacturer's instructions.

- Pattern Writing: Use an EBL system to directly write the electrode pattern onto the resist with a focused electron beam.

- Development: Develop the resist in a suitable developer solution (e.g., a mixture of MIBK and IPA for PMMA).

- Metal Deposition: Deposit the electrode metals as described in the photolithography section.

- Lift-off: Perform the lift-off process in a suitable solvent.

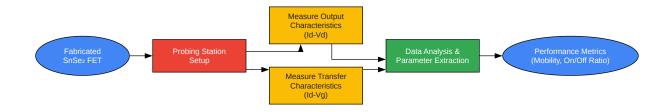

### **Device Characterization**

Electrical characterization is performed to evaluate the performance of the fabricated SnSe<sub>2</sub> FETs.

- Probing: Place the fabricated device on the stage of a probe station.

- Connections: Use micromanipulated probes to make electrical contact with the source, drain, and back-gate (the doped Si substrate).

- Measurements: Use a semiconductor device analyzer or a combination of voltage sources and ammeters to perform the following measurements:

- Output Characteristics (Id-Vd): Measure the drain current (Id) as a function of the drainsource voltage (Vd) for different gate voltages (Vg).

- Transfer Characteristics (Id-Vg): Measure the drain current (Id) as a function of the gate voltage (Vg) at a fixed drain-source voltage (Vd).

- Parameter Extraction: From the measured characteristics, key performance metrics can be extracted:

- o On/Off Ratio: The ratio of the maximum on-state current to the minimum off-state current from the transfer curve.

- Field-Effect Mobility ( $\mu$ ): Calculated from the transconductance (gm = dld/dVg) in the linear region of the transfer curve using the formula:  $\mu$  = [L / (W \* Ci \* Vd)] \* gm, where L is the channel length, W is the channel width, and Ci is the gate capacitance per unit area.

### **Visualized Workflows**

The following diagrams illustrate the key experimental workflows for the fabrication and characterization of SnSe<sub>2</sub>-based FETs.

Click to download full resolution via product page

Caption: Workflow for the fabrication of SnSe<sub>2</sub>-based FETs.

Click to download full resolution via product page

Caption: Workflow for the electrical characterization of SnSe<sub>2</sub> FETs.

#### **Need Custom Synthesis?**

BenchChem offers custom synthesis for rare earth carbides and specific isotopiclabeling.

Email: info@benchchem.com or Request Quote Online.

## References

- 1. pubs.aip.org [pubs.aip.org]

- 2. researchgate.net [researchgate.net]

- 3. pubs.aip.org [pubs.aip.org]

- 4. researchgate.net [researchgate.net]

- 5. researchgate.net [researchgate.net]

- 6. scispace.com [scispace.com]

- To cite this document: BenchChem. [Application Notes and Protocols for Fabricating SnSe<sub>2</sub>-Based Field-Effect Transistors]. BenchChem, [2025]. [Online PDF]. Available at: [https://www.benchchem.com/product/b1590759#fabricating-snse2-based-field-effect-transistors]

#### **Disclaimer & Data Validity:**

The information provided in this document is for Research Use Only (RUO) and is strictly not intended for diagnostic or therapeutic procedures. While BenchChem strives to provide accurate protocols, we make no warranties, express or implied, regarding the fitness of this product for every specific experimental setup.

**Technical Support:**The protocols provided are for reference purposes. Unsure if this reagent suits your experiment? [Contact our Ph.D. Support Team for a compatibility check]

Need Industrial/Bulk Grade? Request Custom Synthesis Quote

# BenchChem

Our mission is to be the trusted global source of essential and advanced chemicals, empowering scientists and researchers to drive progress in science and industry. Contact

Address: 3281 E Guasti Rd

Ontario, CA 91761, United States

Phone: (601) 213-4426

Email: info@benchchem.com