# **Application Notes and Protocols for Boron Doping in Semiconductor Manufacturing**

Author: BenchChem Technical Support Team. Date: December 2025

Audience: Researchers, scientists, and professionals in semiconductor research and development.

Introduction: **Boron** is the most common p-type dopant used in silicon-based semiconductor manufacturing.[1][2][3][4] The precise introduction of **boron** atoms into the silicon crystal lattice creates "holes," which act as positive charge carriers, thereby controlling the electrical conductivity of the material.[4][5][6] This process, known as doping, is a fundamental step in the fabrication of electronic devices such as diodes, transistors, and integrated circuits.[1][7] This document provides detailed application notes and experimental protocols for the primary techniques used for **boron** doping: ion implantation, thermal diffusion, and in-situ doping during epitaxial growth.

## Ion Implantation

Ion implantation is a highly precise and controllable method for introducing dopants into a semiconductor substrate.[5][7][8] It involves accelerating **boron** ions to a high energy and directing them as a beam onto the silicon wafer.[7][9] The ions penetrate the surface and come to rest at a depth determined by their energy.[10][11] This technique offers exceptional control over the dose (number of dopant atoms per unit area) and the depth of the doped region.[8]

#### **Key Applications:**

Formation of shallow source/drain extensions in modern CMOS transistors.

- Precise adjustment of the threshold voltage (Vt) in MOSFETs.[9]

- Creation of complex, non-uniform doping profiles (retrograde wells).

## **Quantitative Data for Boron Ion Implantation**

The following table summarizes typical parameters for **boron** ion implantation in silicon. The process often uses **Boron** Trifluoride (BF<sub>3</sub>) or Diborane (B<sub>2</sub>H<sub>6</sub>) as the ion source.[10] For shallow junctions, the molecular ion BF<sub>2</sub><sup>+</sup> is often used, as it dissociates upon impact, effectively reducing the **boron** implant energy.[12]

| Parameter          | Typical Range                           | Unit      | Notes                                                                                                   |

|--------------------|-----------------------------------------|-----------|---------------------------------------------------------------------------------------------------------|

| Implant Energy     | 0.1 - 200                               | keV       | Lower energies (0.1-<br>10 keV) for shallow<br>junctions; higher<br>energies for deep<br>wells.[10][12] |

| Implant Dose       | 1x10 <sup>11</sup> - 1x10 <sup>16</sup> | atoms/cm² | Low dose for Vt<br>adjust; high dose for<br>source/drain<br>formation.[12][13]                          |

| Peak Concentration | 1x10 <sup>16</sup> - 5x10 <sup>20</sup> | atoms/cm³ | Dependent on dose and energy. Can exceed solid solubility.                                              |

| Junction Depth     | 10 - 500                                | nm        | Controlled primarily by implant energy.                                                                 |

| Tilt Angle         | 3 - 7                                   | degrees   | Used to minimize ion channeling along crystal planes.[10]                                               |

| Wafer Temperature  | Room Temp. to 500                       | °C        | Hot implantation can be used to control surface damage.[9]                                              |

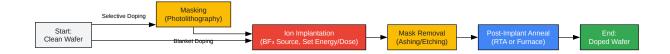

## **Experimental Protocol: Boron Ion Implantation**

This protocol outlines the standard steps for p-type doping of a silicon wafer using ion implantation.

#### 1. Wafer Preparation:

- Start with a clean, n-type silicon wafer.

- If selective doping is required, a masking layer (e.g., photoresist or silicon dioxide) must be patterned on the wafer surface to define the regions to be implanted.

- Perform a pre-implant cleaning step, typically a brief etch in dilute hydrofluoric acid (HF) to remove any native oxide from the implant windows.

#### 2. Implanter Setup:

- Load the wafer into the ion implanter's process chamber.

- Select the **boron** source gas (e.g., BF<sub>3</sub>).

- Set the key process parameters:

- Ion Species: Select the desired ion (e.g., <sup>11</sup>B<sup>+</sup> or <sup>49</sup>BF<sub>2</sub><sup>+</sup>).

- Energy: Set the acceleration energy according to the target junction depth (e.g., 5 keV for a shallow junction).

- Dose: Set the total number of ions to be implanted per unit area (e.g., 5x10<sup>15</sup> cm<sup>-2</sup> for a source/drain region).[14]

- Beam Current: Set the ion beam current, which determines the implantation time (e.g., 1-15 mA).[14]

- Tilt/Twist Angle: Set the wafer orientation relative to the ion beam to prevent channeling (e.g., 7° tilt).[10]

#### 3. Implantation Process:

- Evacuate the process chamber to high vacuum.

- Generate the ion beam, analyze it to select the correct ion species, and accelerate it to the set energy.

- Scan the ion beam across the wafer surface (or move the wafer through a stationary beam)

until the target dose is reached. The system continuously monitors the implanted charge to

determine the dose.[9]

#### 4. Post-Implantation Annealing:

- After implantation, the silicon crystal lattice is damaged and most boron atoms are not in electrically active substitutional sites.

- A high-temperature annealing step is required to repair the crystal damage and "activate" the dopants.

- · Common methods include:

- Rapid Thermal Annealing (RTA): Heat the wafer to a high temperature (e.g., 900-1050°C) for a short time (e.g., 1-60 seconds). This activates the dopants while minimizing their diffusion.

- Furnace Annealing: Heat the wafer in a furnace at a lower temperature for a longer duration (e.g., 900°C for 15-30 minutes).[15]

## **Workflow Diagram: Ion Implantation**

Click to download full resolution via product page

Caption: Workflow for the **boron** ion implantation process.

## **Thermal Diffusion**

Thermal diffusion is a well-established doping technique where dopant atoms are introduced into the silicon wafer at high temperatures (typically 900-1100°C).[16] The process relies on a concentration gradient, causing **boron** atoms to diffuse from a source into the silicon. The surface concentration is often limited by the solid solubility of **boron** in silicon at a given temperature.[17][18]

#### **Key Applications:**

- Formation of deep wells in CMOS processes.

- Doping of p-type emitters in solar cells.[19]

- Creation of heavily doped p+ layers for ohmic contacts.

#### **Diffusion Sources**

**Boron** diffusion can be performed using solid, liquid, or gaseous sources.

- Solid Sources: **Boron** Nitride (BN) wafers are a common solid source.[18] They are placed in proximity to the silicon wafers in a furnace. At high temperatures, B<sub>2</sub>O<sub>3</sub> sublimes from the source and reacts with the silicon surface to form a borosilicate glass (BSG) layer, which then acts as the diffusion source.[18]

- Liquid Sources: **Boron** Tribromide (BBr<sub>3</sub>) is a widely used liquid source.[20][21] A carrier gas (e.g., Nitrogen) is bubbled through the liquid BBr<sub>3</sub>, and the resulting vapor is transported into the diffusion furnace.

- Gaseous Sources: Diborane (B<sub>2</sub>H<sub>6</sub>) is a gaseous source, typically diluted in an inert gas. It is highly toxic and pyrophoric, requiring extensive safety precautions.[16]

## **Quantitative Data for Boron Thermal Diffusion**

| Parameter             | Typical Range                           | Unit      | Notes                                                                               |

|-----------------------|-----------------------------------------|-----------|-------------------------------------------------------------------------------------|

| Diffusion Temperature | 900 - 1100                              | °C        | Higher temperatures result in higher solid solubility and faster diffusion.[22][23] |

| Diffusion Time        | 15 - 120                                | minutes   | Longer times lead to deeper junctions.[18]                                          |

| Surface Concentration | 1x10 <sup>18</sup> - 3x10 <sup>20</sup> | atoms/cm³ | Typically limited by the solid solubility of boron at the process temperature.[17]  |

| Junction Depth        | 0.5 - 10                                | μm        | Generally produces deeper junctions than implantation.                              |

| Sheet Resistance      | 10 - 200                                | Ω/sq      | Dependent on surface concentration and junction depth.                              |

## Experimental Protocol: Two-Step Diffusion from Solid Source (BN)

This protocol describes a common two-step diffusion process: a short "predeposition" step to introduce a controlled amount of dopant near the surface, followed by a longer "drive-in" step to push the dopants deeper into the wafer.

#### 1. Wafer and Furnace Preparation:

- Start with clean, n-type silicon wafers.

- Perform a standard RCA clean or equivalent to remove organic and metallic contaminants.

- If selective doping is needed, grow and pattern a silicon dioxide (SiO<sub>2</sub>) layer to act as a diffusion mask.

- Load the silicon wafers and Boron Nitride (BN) source wafers into a quartz boat, alternating them such that each silicon wafer faces a source wafer.

Ramp the furnace temperature to the target for predeposition (e.g., 950°C) with a steady flow of nitrogen (N<sub>2</sub>).[18]

#### 2. Predeposition Step:

- Once the temperature is stable, push the boat into the center of the furnace.

- Perform the predeposition diffusion for a set time (e.g., 15-30 minutes) in a nitrogen ambient.

[18] During this step, a thin, boron-rich borosilicate glass (BSG) layer forms on the wafer surface.

- Pull the boat from the furnace and allow it to cool.

#### 3. BSG Removal:

- The BSG layer must be removed before the drive-in step.

- Etch the wafers in a dilute hydrofluoric acid (HF) solution (e.g., 10:1 DI water:HF) for 1-2 minutes until the surface is hydrophobic (de-wets).

- Rinse thoroughly with deionized (DI) water and dry with nitrogen.

#### 4. Drive-In Step:

- Reload the silicon wafers (without the BN sources) into a clean furnace tube.

- Ramp the temperature to the drive-in target (e.g., 1100°C).

- Perform the drive-in diffusion for the desired time (e.g., 60 minutes). This step is often done in an oxidizing ambient (O<sub>2</sub> or H<sub>2</sub>O vapor). The growing oxide layer consumes silicon, and the dopants are redistributed and diffused deeper into the bulk.

- Pull the wafers from the furnace and allow them to cool. The final junction depth is determined by both the predeposition and drive-in steps.

## **Workflow Diagram: Two-Step Thermal Diffusion**

Click to download full resolution via product page

Caption: Workflow for a two-step **boron** thermal diffusion process.

## **In-Situ Doping during Epitaxial Growth**

In-situ doping involves introducing the dopant gas during the single-crystal silicon growth (epitaxy) process itself. This allows for the creation of uniformly doped layers with abrupt interfaces and precise thickness control. Chemical Vapor Deposition (CVD) is the most common method for silicon epitaxy.

#### **Key Applications:**

- Growing heavily doped p+ substrate layers for epitaxial wafers.[24]

- Creating complex structures like delta-doped layers or superlattices.

- Forming the base layer in bipolar junction transistors (BJTs).

**Quantitative Data for In-Situ Boron Doping**

| Parameter            | Typical Range                             | Unit      | Notes                                                                                |

|----------------------|-------------------------------------------|-----------|--------------------------------------------------------------------------------------|

| Growth Temperature   | 550 - 1100                                | °C        | Lower temperatures are used in Ultra-High Vacuum CVD (UHV-CVD).                      |

| Dopant Gas           | Diborane (B <sub>2</sub> H <sub>6</sub> ) | -         | Highly diluted in a carrier gas like H2.                                             |

| Dopant Concentration | 1x10 <sup>15</sup> - 5x10 <sup>19</sup>   | atoms/cm³ | Controlled by the partial pressure of the B <sub>2</sub> H <sub>6</sub> gas.[25][26] |

| Growth Rate          | 0.1 - 1.0                                 | μm/min    | Can be affected by the presence of the dopant gas.                                   |

| Layer Thickness      | 0.1 - 100                                 | μm        | Precisely controlled by the growth time.[24]                                         |

## **Experimental Protocol: In-Situ Doping via CVD**

Substrate Preparation:

- 1. Start with a clean silicon substrate wafer.

- 2. Perform a pre-epitaxy clean, often including an HF dip to remove native oxide and passivate the surface with hydrogen.

- Load the substrate into the CVD reactor chamber.

- Epitaxial Growth and Doping:

- 1. Evacuate the chamber and then backfill with a carrier gas (e.g., H<sub>2</sub>).

- 2. Heat the substrate to the target growth temperature (e.g., 650°C).[25]

- 3. Introduce the silicon source gas (e.g., Silane, SiH<sub>4</sub>, or Dichlorosilane, SiH<sub>2</sub>Cl<sub>2</sub>) into the chamber to begin epitaxial growth.

- 4. Simultaneously, introduce a controlled flow of the dopant gas mixture (e.g., B₂H₆ diluted in H₂).[25] The ratio of the dopant gas flow to the silicon source gas flow determines the final **boron** concentration in the grown film.

- 5. Continue the process until the desired layer thickness is achieved. The doping profile is typically very uniform throughout the grown layer.

- · Process Termination:

- 1. Shut off the source and dopant gas flows.

- 2. Cool the wafer down in an inert or H2 ambient.

- 3. Remove the wafer from the chamber. No post-growth annealing is needed for activation, as the **boron** atoms are incorporated into active lattice sites during growth.

## **Workflow Diagram: In-Situ Doping**

Click to download full resolution via product page

Caption: Workflow for in-situ boron doping during CVD epitaxial growth.

**Comparison of Doping Techniques**

| Feature           | lon Implantation                     | Thermal Diffusion             | In-Situ Doping<br>(Epitaxy)      |

|-------------------|--------------------------------------|-------------------------------|----------------------------------|

| Dose Control      | Excellent (Precise, repeatable)      | Fair (Depends on time, temp)  | Good (Depends on gas flow)       |

| Depth Control     | Excellent (Controlled by energy)     | Fair (Depends on time, temp)  | Excellent (Controlled by growth) |

| Profile Shape     | Gaussian (Can be complex)            | erfc or Gaussian<br>(Gradual) | Box-like (Uniform, abrupt)       |

| Throughput        | High (Single wafer processing)       | High (Batch processing)       | Low to Medium                    |

| Crystal Damage    | High (Requires anneal)               | Low                           | Very Low (High quality crystal)  |

| Max Concentration | Can exceed solid solubility          | Limited by solid solubility   | Limited by solid solubility      |

| Conformality      | Line-of-sight<br>(Shadowing effects) | Excellent (Isotropic)         | Excellent (Follows surface)      |

| Thermal Budget    | Low (Implant) + High<br>(Anneal)     | Very High                     | High                             |

| Complexity/Cost   | High                                 | Medium                        | High                             |

#### **Need Custom Synthesis?**

BenchChem offers custom synthesis for rare earth carbides and specific isotopiclabeling.

Email: info@benchchem.com or Request Quote Online.

### References

- 1. Semiconductor Wikipedia [en.wikipedia.org]

- 2. researchgate.net [researchgate.net]

- 3. Doping (semiconductor) Wikipedia [en.wikipedia.org]

- 4. Semiconductors and doping [web.pa.msu.edu]

- 5. agsdevices.com [agsdevices.com]

- 6. m.youtube.com [m.youtube.com]

- 7. universitywafer.com [universitywafer.com]

- 8. What Is Ion Implantation and Why Is It Crucial for Doping? [eureka.patsnap.com]

- 9. Ion implantation Wikipedia [en.wikipedia.org]

- 10. chinsor.com [chinsor.com]

- 11. US8618514B2 Ion implantation device and a method of semiconductor manufacturing by the implantation of boron hydride cluster ions Google Patents [patents.google.com]

- 12. cityu.edu.hk [cityu.edu.hk]

- 13. researchgate.net [researchgate.net]

- 14. axcelis.com [axcelis.com]

- 15. researchgate.net [researchgate.net]

- 16. m.youtube.com [m.youtube.com]

- 17. jhaj.net [jhaj.net]

- 18. ECE Illinois ece444: Boron Predeposition Process [fabweb.ece.illinois.edu]

- 19. chalcogen.ro [chalcogen.ro]

- 20. Concentration dependence of the boron diffusion coefficient in silicon [inis.iaea.org]

- 21. biomedres.us [biomedres.us]

- 22. gtuttle.net [gtuttle.net]

- 23. Solved A constant-source boron diffusion (B is a p dopant) | Chegg.com [chegg.com]

- 24. P Type Boron Doped Silicon Epitaxial Wafer with Low Defect Sensity [powerwaywafer.com]

- 25. mdpi.com [mdpi.com]

- 26. researchgate.net [researchgate.net]

- To cite this document: BenchChem. [Application Notes and Protocols for Boron Doping in Semiconductor Manufacturing]. BenchChem, [2025]. [Online PDF]. Available at: [https://www.benchchem.com/product/b1173376#techniques-for-boron-doping-in-semiconductor-manufacturing]

#### **Disclaimer & Data Validity:**

The information provided in this document is for Research Use Only (RUO) and is strictly not intended for diagnostic or therapeutic procedures. While BenchChem strives to provide accurate protocols, we make no warranties, express or implied, regarding the fitness of this product for every specific experimental setup.

**Technical Support:** The protocols provided are for reference purposes. Unsure if this reagent suits your experiment? [Contact our Ph.D. Support Team for a compatibility check]

Need Industrial/Bulk Grade? Request Custom Synthesis Quote

## BenchChem

Our mission is to be the trusted global source of essential and advanced chemicals, empowering scientists and researchers to drive progress in science and industry.

#### Contact

Address: 3281 E Guasti Rd

Ontario, CA 91761, United States

Phone: (601) 213-4426

Email: info@benchchem.com