# **Application Notes and Protocols for Arsenic Sulfide in Resistive Switching Memory**

Author: BenchChem Technical Support Team. Date: December 2025

| Compound of Interest |                 |           |

|----------------------|-----------------|-----------|

| Compound Name:       | Arsenic sulfide |           |

| Cat. No.:            | B1217354        | Get Quote |

For Researchers, Scientists, and Professionals in Materials Science and Device Engineering

These application notes provide a comprehensive overview of **arsenic sulfide** (AsS) as a functional material for resistive random-access memory (ReRAM). This document details the underlying switching mechanisms, fabrication protocols for thin-film devices, and standardized electrical characterization procedures. The information is intended to serve as a foundational guide for researchers and engineers working on the development of next-generation non-volatile memory technologies.

# Introduction to Arsenic Sulfide-Based Resistive Memory

**Arsenic sulfide**, particularly in its amorphous form (a-As<sub>2</sub>S<sub>3</sub>), is a chalcogenide glass that exhibits resistive switching behavior. This property allows it to function as the active material in a memristor, a two-terminal electrical component whose resistance can be modulated by the history of applied voltage or current. The primary mechanism behind this switching in AsS devices, especially when paired with an electrochemically active electrode like silver (Ag), is the formation and dissolution of conductive filaments within the material.

Devices based on **arsenic sulfide** are categorized as electrochemical metallization (ECM) cells. The application of an electric field causes the oxidation of the active electrode (e.g., Ag), leading to the migration of metal ions (Ag<sup>+</sup>) into the chalcogenide film. These ions are subsequently reduced, forming a metallic filament that bridges the top and bottom electrodes.

This filament creates a low-resistance state (LRS or ON state). Reversing the voltage bias ruptures this filament, returning the device to a high-resistance state (HRS or OFF state). This reversible transition between LRS and HRS is the basis for storing binary data.

## **Performance Metrics of Arsenic Sulfide Memristors**

The performance of **arsenic sulfide**-based resistive switching devices is evaluated based on several key parameters. The table below summarizes typical performance metrics observed in devices with a silver active electrode. These values can vary based on fabrication parameters such as film thickness, deposition method, and electrode materials.

| Performance Metric      | Typical Value Range                      | Description                                                                                           |

|-------------------------|------------------------------------------|-------------------------------------------------------------------------------------------------------|

| ON/OFF Ratio            | 10² - 10 <sup>6</sup>                    | The ratio of the resistance in the high-resistance state (HRS) to the low-resistance state (LRS).     |

| Set Voltage (V_set)     | +0.2 V to +0.8 V                         | The voltage required to switch the device from HRS to LRS.                                            |

| Reset Voltage (V_reset) | -0.1 V to -0.5 V                         | The voltage of opposite polarity required to switch the device from LRS to HRS.                       |

| Endurance               | 10² - 10⁵ cycles                         | The number of times the device can be reliably switched between HRS and LRS before failure.           |

| Data Retention          | > 10 <sup>4</sup> seconds                | The duration for which the device can maintain its resistance state (both HRS and LRS) without power. |

| Switching Speed         | Nanoseconds (ns) to<br>Microseconds (μs) | The time required to perform a SET or RESET operation, typically measured using voltage pulses.       |

## Experimental Protocols Protocol for Device Fabrication: Ag/As<sub>2</sub>S<sub>3</sub>/W Structure

This protocol outlines the fabrication of a common **arsenic sulfide** memristor structure using thermal evaporation and sputtering techniques on a silicon substrate with a tungsten (W) bottom electrode.

#### Materials and Equipment:

- Si wafer with a thermally grown SiO<sub>2</sub> layer (200-300 nm)

- Tungsten (W) target for sputtering

- High-purity **arsenic sulfide** (As<sub>2</sub>S<sub>3</sub>) evaporation material

- High-purity silver (Ag) evaporation material

- Photolithography equipment (photoresist, spinner, mask aligner)

- · Sputtering system

- Thermal evaporation system with a quartz crystal microbalance

- Lift-off solvent (e.g., acetone)

#### Procedure:

- Substrate Preparation:

- Begin with a clean Si/SiO<sub>2</sub> substrate.

- Deposit a 100 nm thick Tungsten (W) film using DC magnetron sputtering to serve as the bottom electrode. An adhesion layer of Titanium (Ti) or Chromium (Cr) (5-10 nm) may be deposited prior to the W layer.

- Patterning the Bottom Electrode (Optional, for isolated devices):

- Use standard photolithography to pattern the bottom electrode into desired shapes (e.g., lines).

- Etch the exposed W film using a suitable etching process (e.g., reactive ion etching).

- Remove the remaining photoresist.

- Deposition of Arsenic Sulfide (As<sub>2</sub>S<sub>3</sub>) Layer:

- Place the substrate in a thermal evaporation chamber.

- Evaporate As<sub>2</sub>S<sub>3</sub> to a thickness of 30-50 nm at a deposition rate of 0.1-0.2 nm/s. The chamber pressure should be maintained below 5 x 10<sup>-6</sup> Torr. Monitor the thickness in-situ using a quartz crystal microbalance.

- Deposition and Patterning of the Top Electrode:

- Use photolithography to create a pattern for the top electrode. This is typically done using a lift-off process.

- Spin-coat a layer of photoresist onto the As<sub>2</sub>S<sub>3</sub> film.

- Expose and develop the photoresist to create openings where the top electrode will be deposited.

- Transfer the substrate to the thermal evaporation system.

- Deposit a 100-150 nm thick Silver (Ag) film.

- Perform the lift-off process by immersing the substrate in a solvent (e.g., acetone) to remove the photoresist and the overlying metal, leaving behind the patterned top electrodes.

- Final Annealing (Optional):

- A post-fabrication anneal in a vacuum or inert atmosphere may be performed to improve film quality and device performance, though it is not always necessary for As<sub>2</sub>S<sub>3</sub> devices.

### **Protocol for Electrical Characterization**

This protocol describes the standard procedure for measuring the resistive switching characteristics of the fabricated As<sub>2</sub>S<sub>3</sub> memristor devices.

#### Equipment:

- Probe station with micro-manipulators

- Semiconductor device analyzer or a source measure unit (SMU) with pulse generation capabilities (e.g., Keithley 4200-SCS, Agilent B1500A).

#### Procedure:

- I-V Characterization (DC Sweep):

- Place the fabricated device on the probe station stage.

- Contact the top (Ag) and bottom (W) electrodes with probes.

- o Apply a DC voltage sweep from 0 V → V\_max → 0 V → V\_min → 0 V. A typical range would be 0 V → 1 V → 0 V → -1 V → 0 V.

- $\circ$  Set a compliance current (e.g., 100  $\mu$ A 1 mA) during the positive (SET) sweep to prevent permanent dielectric breakdown of the device.

- Record the current as a function of the applied voltage to obtain the characteristic pinched hysteresis loop.

- From the I-V curve, extract the V\_set, V\_reset, HRS, and LRS values.

- Endurance Testing (Pulsed Measurement):

- Apply a sequence of alternating positive (SET) and negative (RESET) voltage pulses.

- Typical SET pulse: +1 V to +2 V amplitude, 100 ns to 1 μs pulse width.

- Typical RESET pulse: -0.8 V to -1.5 V amplitude, 100 ns to 1 μs pulse width.

- After each SET and RESET pulse, apply a small read voltage (e.g., 0.1 V) to measure the resistance state without disturbing it.

- Repeat this cycle for at least 10<sup>3</sup> times and plot the HRS and LRS values against the cycle number to evaluate endurance.

- Retention Testing:

- Switch the device to the LRS using a SET pulse.

- Periodically measure the resistance at a low read voltage (0.1 V) over an extended period (e.g., 10<sup>4</sup> seconds or more) at a specific temperature (e.g., room temperature or 85°C).

- Switch the device to the HRS using a RESET pulse and repeat the periodic resistance measurement.

- Plot the resistance of both states as a function of time to assess data retention.

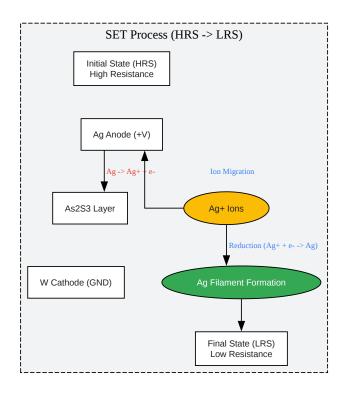

# Visualizations Switching Mechanism

The diagram below illustrates the electrochemical metallization mechanism responsible for resistive switching in a Ag/As<sub>2</sub>S<sub>3</sub>/W device.

Click to download full resolution via product page

Resistive switching mechanism in Ag/As<sub>2</sub>S<sub>3</sub>/W devices.

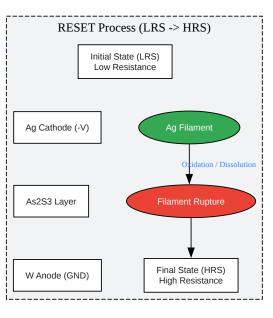

## **Fabrication Workflow**

The following diagram outlines the key steps in the fabrication of an **arsenic sulfide** memristor device using a lift-off process for the top electrode.

Click to download full resolution via product page

Device fabrication workflow using photolithography and lift-off.

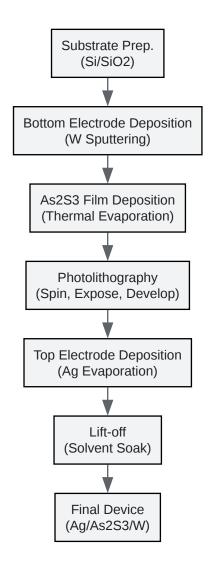

## **Electrical Characterization Logic**

This diagram shows the logical flow for the complete electrical testing of a fabricated **arsenic** sulfide memristor.

Click to download full resolution via product page

To cite this document: BenchChem. [Application Notes and Protocols for Arsenic Sulfide in Resistive Switching Memory]. BenchChem, [2025]. [Online PDF]. Available at: [https://www.benchchem.com/product/b1217354#arsenic-sulfide-as-a-resistive-switching-memory-material]

#### **Disclaimer & Data Validity:**

The information provided in this document is for Research Use Only (RUO) and is strictly not intended for diagnostic or therapeutic procedures. While BenchChem strives to provide accurate protocols, we make no warranties, express or implied, regarding the fitness of this product for every specific experimental setup.

**Technical Support:** The protocols provided are for reference purposes. Unsure if this reagent suits your experiment? [Contact our Ph.D. Support Team for a compatibility check]

Need Industrial/Bulk Grade? Request Custom Synthesis Quote

## BenchChem

Our mission is to be the trusted global source of essential and advanced chemicals, empowering scientists and researchers to drive progress in science and industry. Contact

Address: 3281 E Guasti Rd

Ontario, CA 91761, United States

Phone: (601) 213-4426

Email: info@benchchem.com