# Application Notes and Protocols: Silicon Nitride as a Gate Dielectric in GaN HEMTs

Author: BenchChem Technical Support Team. Date: December 2025

For Researchers, Scientists, and Drug Development Professionals

### Introduction

Gallium Nitride (GaN) High Electron Mobility Transistors (HEMTs) are at the forefront of next-generation power electronics and radio frequency (RF) applications, owing to their superior material properties such as a wide bandgap, high breakdown electric field, and high electron mobility. However, the performance and reliability of GaN HEMTs are significantly influenced by surface states and trapping effects, which can lead to phenomena like current collapse and increased gate leakage. **Silicon Nitride** (SiN) has emerged as a critical material for both surface passivation and as a gate dielectric in GaN HEMTs to mitigate these issues.

This document provides a detailed overview of the application of SiN as a gate dielectric in GaN HEMTs, including its material properties, common deposition methods, and its impact on device performance. Furthermore, it offers comprehensive, step-by-step experimental protocols for the deposition and characterization of SiN layers in the context of GaN HEMT fabrication and analysis.

### The Role of Silicon Nitride in GaN HEMTs

Silicon nitride serves two primary functions in GaN HEMT technology:

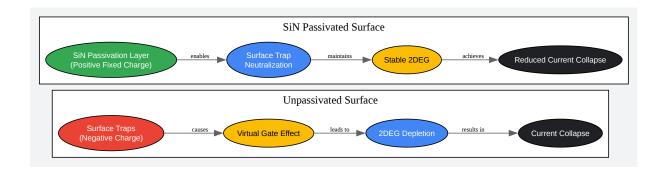

Surface Passivation: The surface of the AlGaN barrier layer in a GaN HEMT is prone to trapping electrons, which can create a "virtual gate" that depletes the two-dimensional

electron gas (2DEG) channel. This leads to a dynamic increase in on-resistance, a phenomenon known as current collapse. A SiN passivation layer can effectively neutralize these surface traps, thereby stabilizing the 2DEG and significantly reducing current collapse. [1][2] The stoichiometry of the SiN film can be tuned to optimize passivation and minimize device degradation.[1]

Gate Dielectric: By incorporating a SiN layer directly beneath the gate metal, a Metal-Insulator-Semiconductor HEMT (MIS-HEMT) structure is formed. This SiN gate dielectric serves to suppress the gate leakage current, which is a significant challenge in conventional Schottky gate HEMTs.[3][4] This reduction in gate leakage allows for a larger gate voltage swing, improving the device's overall efficiency and reliability. The use of a SiN gate insulator is a key step in fabricating robust GaN power devices.[3]

## **Deposition Methods for Silicon Nitride**

The two most prevalent methods for depositing SiN films for GaN HEMT applications are Plasma-Enhanced Chemical Vapor Deposition (PECVD) and Low-Pressure Chemical Vapor Deposition (LPCVD).

## **Plasma-Enhanced Chemical Vapor Deposition (PECVD)**

PECVD is a widely used technique due to its relatively low deposition temperatures (typically 300-400°C), which are compatible with GaN device processing.[5][6] In this process, precursor gases, typically silane (SiH<sub>4</sub>) and ammonia (NH<sub>3</sub>) diluted in nitrogen (N<sub>2</sub>), are introduced into a chamber where a plasma is generated. The plasma energizes the gas molecules, allowing the SiN film to form on the substrate at a lower temperature than in thermal CVD processes. The properties of the PECVD SiN film, such as stoichiometry, stress, and density, can be tailored by adjusting process parameters like temperature, pressure, RF power, and gas flow rates.[6]

## **Low-Pressure Chemical Vapor Deposition (LPCVD)**

LPCVD is another common method for SiN deposition, typically carried out at higher temperatures (600-800°C) and lower pressures than PECVD.[7] The precursor gases, often dichlorosilane (SiH<sub>2</sub>Cl<sub>2</sub>) and ammonia (NH<sub>3</sub>), react on the heated substrate surface to form a stoichiometric and dense SiN film.[7] LPCVD SiN films are known for their excellent uniformity, high purity, and superior dielectric properties.[7] The higher deposition temperature generally

results in films with lower hydrogen content and higher thermal stability compared to PECVD SiN.[8]

# Data Presentation: Properties and Performance Comparison

The choice of SiN deposition method and the resulting film properties have a direct impact on the performance of GaN HEMTs. The following tables summarize key quantitative data for SiN films and their effect on device characteristics.

Table 1: Comparison of Silicon Nitride Film Properties

| Property                  | PECVD SiN                             | LPCVD SiN         | Unit  |

|---------------------------|---------------------------------------|-------------------|-------|

| Deposition<br>Temperature | 300 - 400                             | 600 - 850         | °C    |

| Dielectric Constant       | ~7                                    | 7 - 7.5           | -     |

| Breakdown Field           | 3 - 9                                 | ~13               | MV/cm |

| Refractive Index          | 1.9 - 2.0                             | ~2.0              | -     |

| Film Stress               | Can be tuned (tensile or compressive) | Typically tensile | МРа   |

| Hydrogen Content          | Significant (Si-H, N-H bonds)         | Very low          | -     |

Table 2: Impact of SiN Gate Dielectric on GaN HEMT Performance

| Parameter                       | Without SiN<br>Passivation | With PECVD<br>SiN<br>Passivation | With LPCVD<br>SiN<br>Passivation | Unit                              |

|---------------------------------|----------------------------|----------------------------------|----------------------------------|-----------------------------------|

| Current Collapse                | Severe                     | Significantly<br>Reduced         | Effectively<br>Suppressed        | %                                 |

| Gate Leakage<br>Current         | High                       | Reduced by orders of magnitude   | Significantly<br>Reduced         | A/mm                              |

| Breakdown<br>Voltage            | ~50 V<br>(unpassivated)    | > 50 V (can be optimized)        | Can reach > 800<br>V             | V                                 |

| Interface Trap<br>Density (Dit) | -                          | 1011 - 1013                      | 1011 - 1012                      | cm <sup>-2</sup> eV <sup>-1</sup> |

| Dynamic On-<br>Resistance (Ron) | High and unstable          | Lower and more stable            | Low and stable                   | Ω·mm                              |

## **Experimental Protocols**

This section provides detailed protocols for key experiments related to the deposition and characterization of SiN as a gate dielectric in GaN HEMTs.

## Protocol 1: PECVD of Silicon Nitride on GaN HEMT Wafers

Objective: To deposit a high-quality SiN film on an AlGaN/GaN HEMT wafer for surface passivation and as a gate dielectric.

Materials and Equipment:

- AlGaN/GaN HEMT wafer

- PECVD system (e.g., Oxford Instruments PlasmaLab100)

- Silane (SiH<sub>4</sub>) gas source

- Ammonia (NH₃) gas source

- Nitrogen (N<sub>2</sub>) gas source

- Wafer handling tools

- Standard cleaning solvents (Acetone, Isopropanol, DI water)

- Acid solutions (e.g., HCl:H<sub>2</sub>O)

- UV-Ozone cleaner

- Wafer Cleaning: a. Perform a solvent clean by sequentially sonicating the wafer in acetone, isopropanol, and deionized (DI) water for 5 minutes each. b. Dry the wafer with a nitrogen gun. c. Perform a UV-Ozone clean for 10 minutes to remove organic residues. d. Dip the wafer in a diluted HCI solution (e.g., 1:10 HCI:H<sub>2</sub>O) for 30 seconds to remove native oxides.

[9] e. Rinse thoroughly with DI water and dry with a nitrogen gun.

- PECVD System Preparation: a. Vent the PECVD chamber and load the cleaned GaN HEMT wafer onto the substrate holder (platen). b. Pump down the chamber to the base pressure (typically < 5 mTorr). c. Heat the substrate to the desired deposition temperature (e.g., 300°C).[10]</li>

- SiN Deposition: a. Introduce the precursor gases into the chamber. A typical recipe is:[10]

- SiH<sub>4</sub> flow rate: 20 sccm

NH<sub>3</sub> flow rate: 23.5 sccm

- N<sub>2</sub> flow rate: 980 sccm b. Set the chamber pressure to 650 mTorr.[10] c. Apply RF power (e.g., 20 W) to generate the plasma.[10] For mixed-frequency PECVD, alternate between high frequency (13.56 MHz) and low frequency (100-360 kHz) to control film stress.[9][10] d. Deposit the SiN film to the desired thickness. The deposition rate is typically around 12 nm/min.[10]

- Post-Deposition: a. Turn off the RF power and gas flows. b. Cool down the substrate to room temperature under vacuum. c. Vent the chamber and unload the wafer.

### Protocol 2: LPCVD of Silicon Nitride on GaN Devices

Objective: To deposit a high-density, low-hydrogen SiN film suitable for high-performance GaN MIS-HEMTs.

#### Materials and Equipment:

- GaN HEMT wafer or test structure

- LPCVD furnace

- Dichlorosilane (SiH2Cl2) gas source

- Ammonia (NH₃) gas source

- Nitrogen (N<sub>2</sub>) gas source

- Wafer boat and handling tools

- Standard cleaning solvents and acids

- Wafer Cleaning: a. Follow a rigorous cleaning procedure similar to the PECVD protocol (Step 1a-e), often concluding with a standard RCA clean.[11]

- LPCVD Furnace Preparation: a. Load the cleaned wafers into a quartz boat. b. Insert the boat into the LPCVD furnace tube. c. Pump down the furnace to the base pressure (typically < 10 mTorr). d. Ramp up the temperature to the deposition temperature (e.g., 770°C).[12]</li>

- SiN Deposition: a. Introduce the precursor gases, dichlorosilane and ammonia, into the furnace. The ratio of these gases is critical for controlling the film's stoichiometry and stress. A common DCS:NH<sub>3</sub> ratio is 3:1.[12] b. Maintain a low process pressure (e.g., 150 mTorr).

[12] c. The deposition is thermally driven; no plasma is used. d. Deposit the SiN film to the desired thickness. Deposition rates are typically lower than in PECVD.

- Post-Deposition: a. After deposition, purge the furnace with nitrogen gas.[13] b. Ramp down the temperature. c. Once at a safe handling temperature, unload the wafers from the

furnace.

# Protocol 3: Capacitance-Voltage (C-V) Measurement for Interface Trap Density (Dit) Extraction

Objective: To determine the density of traps at the SiN/AlGaN interface using C-V measurements on a MIS-HEMT or a test capacitor structure.

#### Materials and Equipment:

- Fabricated GaN MIS-HEMT or MIS capacitor with SiN dielectric

- Semiconductor parameter analyzer with C-V measurement capability (e.g., Keysight B1500A)

- Probe station with temperature-controlled chuck

- Coaxial probes

- Device Setup: a. Place the device on the probe station chuck. b. Make electrical contact to the gate and the source/channel (for a MIS-HEMT) or the bottom contact (for a MIS capacitor) using the probes.

- C-V Measurement: a. Set the measurement parameters on the semiconductor analyzer:

- Frequency: Typically perform sweeps at a high frequency (e.g., 1 MHz) and a low or quasistatic frequency.

- Voltage sweep range: Sweep the gate voltage from accumulation to depletion (e.g., from a positive voltage to a negative voltage for a depletion-mode device).

- AC signal level: Use a small AC signal (e.g., 30-50 mV). b. Perform the C-V sweep and record the capacitance as a function of the applied DC gate voltage.

- Interface Trap Density (Dit) Calculation (Terman Method):[14] a. Ideal C-V Curve Calculation:

Calculate the ideal (trap-free) high-frequency C-V curve based on the known device

parameters (dielectric thickness, doping concentrations, etc.). b. Voltage Shift (ΔV): For a

given capacitance value on the experimental high-frequency C-V curve, find the

### Methodological & Application

corresponding gate voltage (Vg,exp). On the ideal C-V curve, find the gate voltage (Vg,ideal) that gives the same capacitance. The voltage shift is  $\Delta V = Vg$ ,exp - Vg,ideal. c. Dit Calculation: The interface trap density can be calculated using the following formula: Dit =  $(Cox / q^2) * (d(\Delta V) / d\psi s)$  where Cox is the oxide (SiN) capacitance per unit area, q is the elementary charge, and  $\psi s$  is the surface potential. The relationship between gate voltage and surface potential is needed to complete the calculation.[15]

Alternative Method: Conductance Method: The conductance method, which involves measuring the equivalent parallel conductance as a function of frequency and bias, is often more sensitive for determining Dit.[16][17]

## **Protocol 4: Breakdown Voltage Measurement**

Objective: To determine the off-state breakdown voltage of a GaN HEMT with a SiN gate dielectric.

#### Materials and Equipment:

- Fabricated GaN HEMT

- High-voltage source-measure unit (SMU) or curve tracer

- Probe station

- Device Setup: a. Place the device on the probe station. b. Contact the gate, drain, and source terminals with appropriate high-voltage probes.

- Off-State Breakdown Measurement: a. Apply a gate voltage that is sufficiently negative to pinch off the channel (e.g., VGS = Vth 2V). The source is typically grounded. b. Sweep the drain voltage (VDS) from 0 V upwards while monitoring the drain current (ID). c. Breakdown Definition: The breakdown voltage is defined as the drain voltage at which the drain current reaches a predefined critical value, often 1 μA/mm or 1 mA/mm of gate width, before a sudden, irreversible increase in current occurs.[18][19] d. It is crucial to set a current compliance on the SMU to prevent catastrophic failure of the device.

• Data Recording: a. Record the VDS at which the breakdown criterion is met. b. It is often useful to plot the drain leakage current on a logarithmic scale against the drain voltage to clearly identify the breakdown point.

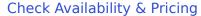

## Mandatory Visualizations GaN HEMT with SiN Gate Dielectric

Click to download full resolution via product page

Caption: Structure of a GaN HEMT with a SiN gate dielectric.

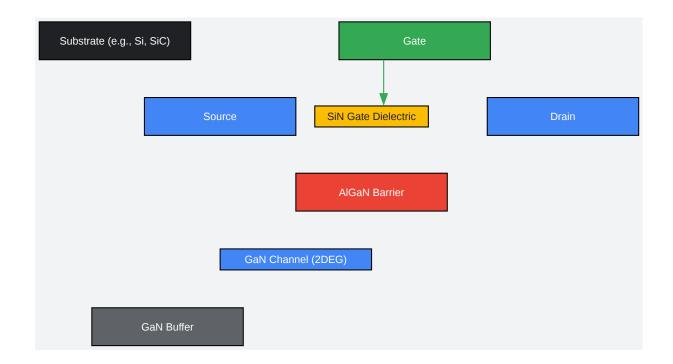

## **Experimental Workflow for SiN Deposition and Characterization**

Click to download full resolution via product page

Caption: Workflow for SiN deposition and GaN HEMT characterization.

## **SiN Passivation Mechanism**

Click to download full resolution via product page

Caption: How SiN passivation mitigates current collapse in GaN HEMTs.

#### **Need Custom Synthesis?**

BenchChem offers custom synthesis for rare earth carbides and specific isotopiclabeling.

Email: info@benchchem.com or Request Quote Online.

### References

- 1. Impact of SiN Passivation on Dynamic-RON Degradation of 100 V p-GaN Gate AlGaN/GaN HEMTs | MDPI [mdpi.com]

- 2. researchgate.net [researchgate.net]

- 3. homepages.laas.fr [homepages.laas.fr]

- 4. AlGaN/GaN MIS-HEMT with PECVD SiNx, SiON, SiO2 as Gate Dielectric and Passivation Layer [mdpi.com]

- 5. fbh-berlin.de [fbh-berlin.de]

- 6. electrochem.org [electrochem.org]

- 7. crystec.com [crystec.com]

- 8. researchgate.net [researchgate.net]

- 9. csmantech.org [csmantech.org]

- 10. csmantech.org [csmantech.org]

- 11. pubs.aip.org [pubs.aip.org]

- 12. publications.lib.chalmers.se [publications.lib.chalmers.se]

- 13. US6147013A Method of LPCVD silicon nitride deposition Google Patents [patents.google.com]

- 14. pubs.aip.org [pubs.aip.org]

- 15. pubs.aip.org [pubs.aip.org]

- 16. A quantitative approach for trap analysis between Al0.25Ga0.75N and GaN in high electron mobility transistors - PMC [pmc.ncbi.nlm.nih.gov]

- 17. Trap Characterization Techniques for GaN-Based HEMTs: A Critical Review [mdpi.com]

- 18. arxiv.org [arxiv.org]

- 19. researchgate.net [researchgate.net]

- To cite this document: BenchChem. [Application Notes and Protocols: Silicon Nitride as a

Gate Dielectric in GaN HEMTs]. BenchChem, [2025]. [Online PDF]. Available at:

[https://www.benchchem.com/product/b078792#silicon-nitride-as-a-gate-dielectric-in-gan-hemts]

#### **Disclaimer & Data Validity:**

The information provided in this document is for Research Use Only (RUO) and is strictly not intended for diagnostic or therapeutic procedures. While BenchChem strives to provide accurate protocols, we make no warranties, express or implied, regarding the fitness of this product for every specific experimental setup.

**Technical Support:**The protocols provided are for reference purposes. Unsure if this reagent suits your experiment? [Contact our Ph.D. Support Team for a compatibility check]

Need Industrial/Bulk Grade? Request Custom Synthesis Quote

## BenchChem

Our mission is to be the trusted global source of essential and advanced chemicals, empowering scientists and researchers to drive progress in science and industry. Contact

Address: 3281 E Guasti Rd

Ontario, CA 91761, United States

Phone: (601) 213-4426

Email: info@benchchem.com