# Application Notes and Protocols: Lanthanum Oxide as a Gate Dielectric in Electronic Devices

Author: BenchChem Technical Support Team. Date: December 2025

For Researchers, Scientists, and Drug Development Professionals

### Introduction

**Lanthanum oxide** (La<sub>2</sub>O<sub>3</sub>) has emerged as a promising high-k gate dielectric material for next-generation complementary metal-oxide-semiconductor (CMOS) devices. Its high dielectric constant ( $k \approx 20\text{-}27$ ), large bandgap ( $\approx 5.8 \text{ eV}$ ), and good thermal stability make it a potential replacement for silicon dioxide (SiO<sub>2</sub>) in scaled-down transistors, enabling further miniaturization and improved performance.[1][2][3] These application notes provide a comprehensive overview of the properties, deposition, characterization, and application of La<sub>2</sub>O<sub>3</sub> as a gate dielectric, along with detailed experimental protocols for researchers in the field.

### **Data Presentation**

The following tables summarize the key electrical and physical properties of **lanthanum oxide** gate dielectrics from various literature sources.

Table 1: Electrical Properties of Lanthanum Oxide (La<sub>2</sub>O<sub>3</sub>) Gate Dielectrics

| Parameter                          | Reported<br>Value(s)                                                              | Deposition<br>Method | Substrate | Notes                                                                                | Reference(s           |

|------------------------------------|-----------------------------------------------------------------------------------|----------------------|-----------|--------------------------------------------------------------------------------------|-----------------------|

| Dielectric<br>Constant (k)         | 20 - 27                                                                           | ALD, PVD,<br>MOCVD   | Si, GaAs  | Value can be affected by crystallinity, interfacial layers, and moisture absorption. | [1][2][4][5][6]       |

| Equivalent Oxide Thickness (EOT)   | 0.48 nm - 1.5<br>nm                                                               | ALD, PVD             | Si        | Lower EOT values are critical for device scaling.                                    | [7][8][9]             |

| Leakage<br>Current<br>Density (Jg) | 10 <sup>-2</sup> - 10 <sup>-7</sup><br>A/cm <sup>2</sup> at 1V                    | ALD, PVD             | Si        | Lower leakage is a key advantage over thin SiO <sub>2</sub> .                        | [7][8][9][10]<br>[11] |

| Breakdown<br>Field (Ebd)           | 4.2 - 13.5<br>MV/cm                                                               | ALD, PVD             | Si        | High breakdown field indicates good dielectric strength.                             | [4][7][8][9]          |

| Interface Trap<br>Density (Dit)    | 3x10 <sup>10</sup> -<br>1.2x10 <sup>12</sup><br>eV <sup>-1</sup> cm <sup>-2</sup> | ALD,<br>Sputtering   | Si, GaAs  | Lower Dit is crucial for good transistor performance.                                | [6][7][8][9]          |

Table 2: Physical Properties of Lanthanum Oxide (La<sub>2</sub>O<sub>3</sub>)

| Property          | Value                        | Notes                                                                       | Reference(s) |

|-------------------|------------------------------|-----------------------------------------------------------------------------|--------------|

| Band Gap (Eg)     | ~5.8 eV                      | A wide band gap<br>helps to reduce<br>leakage current.                      | [1]          |

| Crystal Structure | Amorphous or Polycrystalline | The crystalline phase can influence the dielectric constant.                | [2][4]       |

| Hygroscopicity    | High                         | Absorbs moisture from the air, which can degrade its dielectric properties. | [1][2]       |

## **Experimental Protocols**

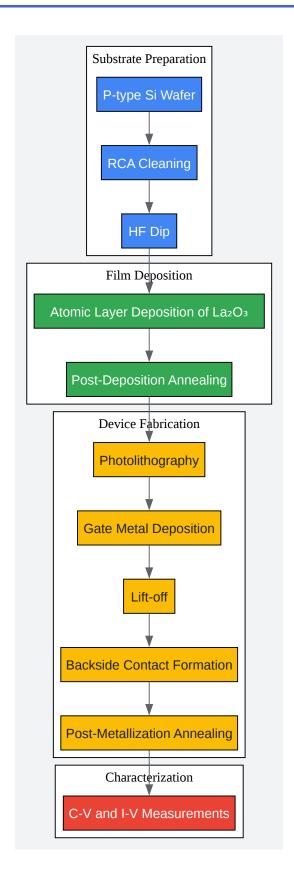

# Protocol 1: Atomic Layer Deposition (ALD) of Lanthanum Oxide

This protocol describes a typical ALD process for depositing thin films of La<sub>2</sub>O<sub>3</sub> on a silicon substrate.

#### Materials and Equipment:

- P-type silicon (100) wafers

- Lanthanum precursor (e.g., tris(N,N'-diisopropylformamidinato)lanthanum [La(iPrfAMD)₃] or La(thd)₃-DMEA)

- Oxidant (e.g., O₃ or H₂O vapor)

- High-purity nitrogen (N2) gas

- ALD reactor

#### Procedure:

• Substrate Preparation:

- 1. Perform a standard RCA clean of the silicon wafers to remove organic and metallic contaminants.

- 2. Dip the wafers in a dilute hydrofluoric acid (HF) solution to remove the native oxide layer.

- 3. Immediately load the wafers into the ALD reactor to minimize re-oxidation.

- ALD Process:

- Heat the La precursor to its optimal sublimation temperature (e.g., 150 °C for La(thd)₃-DMEA).[12]

- 2. Set the substrate temperature within the ALD window (e.g., 200-250 °C).[12]

- 3. Introduce the La precursor into the reactor chamber for a set pulse time (e.g., 8 seconds). [12]

- 4. Purge the chamber with N<sub>2</sub> gas to remove any unreacted precursor and byproducts (e.g., 45 seconds).[12]

- 5. Introduce the oxidant (e.g., O₃) into the chamber for a set pulse time (e.g., 100 milliseconds).[12]

- 6. Purge the chamber with N<sub>2</sub> gas (e.g., 10 seconds).[12]

- Repeat this cycle until the desired film thickness is achieved. The growth rate is typically around 0.4 Å/cycle.[12]

- Post-Deposition Annealing (PDA):

- 1. Perform PDA in a nitrogen atmosphere at a temperature between 400 °C and 800 °C to improve the film quality and reduce defects.[9][13]

# Protocol 2: Fabrication of a Metal-Oxide-Semiconductor Capacitor (MOSCAP)

This protocol outlines the steps to fabricate a MOSCAP for electrical characterization of the  $La_2O_3$  gate dielectric.

#### Materials and Equipment:

- Silicon wafer with La<sub>2</sub>O<sub>3</sub> film

- Metal for gate electrode (e.g., Aluminum, Tungsten)

- Photolithography equipment and materials (photoresist, developer, mask)

- Metal deposition system (e.g., sputtering or evaporation)

- Wet etching chemicals (e.g., appropriate metal etchant)

- Probe station and semiconductor parameter analyzer

#### Procedure:

- Gate Electrode Patterning:

- 1. Spin-coat a layer of photoresist onto the La<sub>2</sub>O<sub>3</sub> film.

- 2. Expose the photoresist to UV light through a photomask defining the gate electrode areas.

- 3. Develop the photoresist to create the desired pattern.

- Gate Metal Deposition:

- 1. Deposit a layer of the chosen gate metal over the patterned photoresist using sputtering or evaporation.

- Lift-off:

- 1. Immerse the wafer in a suitable solvent (e.g., acetone) to dissolve the remaining photoresist, lifting off the metal on top of it and leaving the patterned metal gate electrodes.

- Backside Contact:

- 1. Etch the backside of the wafer with HF to remove any oxide.

- 2. Deposit a layer of aluminum on the backside to form an ohmic contact.

- Post-Metallization Annealing (PMA):

- 1. Perform PMA in a forming gas (e.g., 95% N<sub>2</sub>, 5% H<sub>2</sub>) atmosphere at around 400 °C to improve the metal-semiconductor contact and passivate interface traps.

### **Protocol 3: Electrical Characterization**

Capacitance-Voltage (C-V) Measurement:

- Place the fabricated MOSCAP on the probe station.

- Connect the probes to the gate electrode and the backside contact.

- Using a semiconductor parameter analyzer, sweep the gate voltage from accumulation to inversion and back, while measuring the capacitance at a high frequency (e.g., 1 MHz).

- From the C-V curve, extract key parameters such as the oxide capacitance (Cox), flat-band voltage (Vfb), and interface trap density (Dit).

Current-Voltage (I-V) Measurement:

- With the same setup, sweep the gate voltage and measure the corresponding leakage current through the gate dielectric.

- Plot the leakage current density (Jg) versus the applied electric field to determine the breakdown field.

## **Mandatory Visualization**

Click to download full resolution via product page

Caption: Experimental workflow for fabricating and characterizing La<sub>2</sub>O<sub>3</sub>-based MOS capacitors.

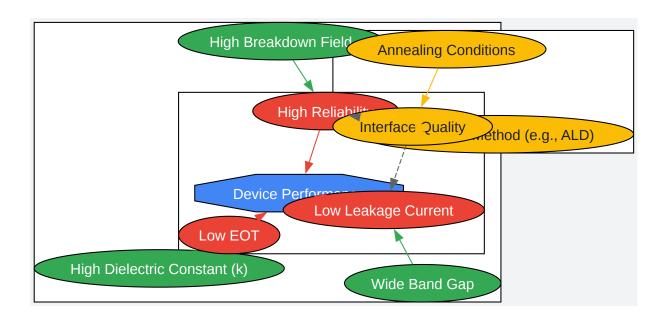

Click to download full resolution via product page

Caption: Logical relationships between material properties, process parameters, and device performance.

#### **Need Custom Synthesis?**

BenchChem offers custom synthesis for rare earth carbides and specific isotopiclabeling.

Email: info@benchchem.com or Request Quote Online.

## References

- 1. web.mit.edu [web.mit.edu]

- 2. researchgate.net [researchgate.net]

- 3. pmc.ncbi.nlm.nih.gov [pmc.ncbi.nlm.nih.gov]

- 4. [PDF] XPS Study of the Bonding Properties of Lanthanum Oxide/Silicon Interface with a Trace Amount of Nitrogen Incorporation | Semantic Scholar [semanticscholar.org]

- 5. medium.com [medium.com]

- 6. researchgate.net [researchgate.net]

- 7. Practical Guide to DOT Language (Graphviz) for Developers and Analysts · while true do; [danieleteti.it]

- 8. DOT Language | Graphviz [graphviz.org]

- 9. jos.ac.cn [jos.ac.cn]

- 10. scribd.com [scribd.com]

- 11. researchgate.net [researchgate.net]

- 12. mdpi.com [mdpi.com]

- 13. researchgate.net [researchgate.net]

- To cite this document: BenchChem. [Application Notes and Protocols: Lanthanum Oxide as a

Gate Dielectric in Electronic Devices]. BenchChem, [2025]. [Online PDF]. Available at:

[https://www.benchchem.com/product/b073253#lanthanum-oxide-as-a-gate-dielectric-inelectronic-devices]

#### **Disclaimer & Data Validity:**

The information provided in this document is for Research Use Only (RUO) and is strictly not intended for diagnostic or therapeutic procedures. While BenchChem strives to provide accurate protocols, we make no warranties, express or implied, regarding the fitness of this product for every specific experimental setup.

**Technical Support:** The protocols provided are for reference purposes. Unsure if this reagent suits your experiment? [Contact our Ph.D. Support Team for a compatibility check]

Need Industrial/Bulk Grade? Request Custom Synthesis Quote

## BenchChem

Our mission is to be the trusted global source of essential and advanced chemicals, empowering scientists and researchers to drive progress in science and industry. Contact

Address: 3281 E Guasti Rd

Ontario, CA 91761, United States

Phone: (601) 213-4426

Email: info@benchchem.com