# Application Notes & Protocols: Fabrication of Organic Thin-Film Transistors with Thiophene Compounds

Author: BenchChem Technical Support Team. Date: December 2025

| Compound of Interest |                                         |           |

|----------------------|-----------------------------------------|-----------|

| Compound Name:       | 4,9-Dimethylnaphtho[2,3-<br>b]thiophene |           |

| Cat. No.:            | B098931                                 | Get Quote |

#### Introduction

Organic thin-film transistors (OTFTs) are fundamental components in the field of organic electronics, offering advantages such as low-temperature fabrication, flexibility, and low cost.[1] Thiophene-based organic semiconductors are a prominent class of materials used in OTFTs due to their excellent charge transport properties and environmental stability.[2][3] Compounds like poly(3-hexylthiophene) (P3HT), dinaphtho[2,3-b:2',3'-f]thieno[3,2-b]thiophene (DNTT), and various oligofluorene-thiophene derivatives have demonstrated high performance in OTFT devices.[4][5] The performance of these devices, characterized by metrics such as charge carrier mobility, on/off current ratio, and threshold voltage, is highly dependent on the molecular structure of the semiconductor, the fabrication process, and the device architecture.[6][7]

This document provides detailed protocols for the fabrication of OTFTs using thiophene-based compounds, focusing on solution-based processing techniques. It is intended for researchers and scientists in materials science and electronics.

#### **Key Performance Parameters**

The efficacy of an OTFT is primarily evaluated by three key parameters:

- Field-Effect Mobility (μ): Represents how quickly charge carriers (holes in p-type semiconductors) move through the semiconductor film under an applied electric field. Higher mobility leads to faster device operation.

- On/Off Current Ratio (Ion/Ioff): The ratio of the drain current when the transistor is in the "on" state to the current when it is in the "off" state. A high ratio is crucial for digital logic applications to distinguish between states.[8]

- Threshold Voltage (Vth): The minimum gate voltage required to turn the transistor "on" and allow current to flow. A low threshold voltage is desirable for low-power applications.

# Experimental Protocols Protocol 1: Substrate Cleaning

A pristine substrate surface is critical for the fabrication of high-performance devices.[9] The following is a standard cleaning procedure for silicon wafers with a silicon dioxide (SiO<sub>2</sub>) dielectric layer.

# Materials:

- Silicon wafers with a thermally grown SiO<sub>2</sub> layer

- Deionized (DI) water

- Acetone (semiconductor grade)

- Isopropyl alcohol (IPA, semiconductor grade)

- Nitrogen (N<sub>2</sub>) gas source

- Ultrasonic bath

- Substrate rack

## Procedure:

Place the Si/SiO<sub>2</sub> substrates in a substrate rack.

- Perform sequential ultrasonic treatments by immersing the rack in beakers containing the following solvents, in order:

- Acetone for 15 minutes.

- Isopropyl alcohol for 15 minutes.[10]

- Deionized water for 15 minutes.

- After the final sonication, thoroughly rinse the substrates with DI water.

- Dry the substrates using a stream of high-purity nitrogen gas.

- Heat the substrates on a hotplate at 100-120 °C for 10 minutes to remove any residual moisture.[10]

# Protocol 2: Surface Treatment with Self-Assembled Monolayers (SAMs)

Treating the dielectric surface can improve the ordering of the organic semiconductor film and enhance device performance. Octadecyltrichlorosilane (OTS) is commonly used to create a hydrophobic surface, which promotes better molecular packing of many thiophene compounds. [10]

#### Materials:

- Cleaned Si/SiO<sub>2</sub> substrates

- Toluene (anhydrous)

- Octadecyltrichlorosilane (OTS) solution (e.g., 10 mM in anhydrous toluene)

- Vacuum oven or glovebox

### Procedure:

• Transfer the cleaned and dried substrates into a nitrogen-filled glovebox.

- Immerse the substrates in the OTS solution for 30 minutes.

- Rinse the substrates sequentially with fresh toluene to remove excess OTS.

- Dry the substrates with a stream of nitrogen gas.

- Anneal the substrates in a vacuum oven at 120 °C for 1 hour to complete the self-assembly process.

# **Protocol 3: Thin-Film Deposition via Spin-Coating**

Spin-coating is a widely used solution-based technique for depositing uniform thin films of organic semiconductors.[11][12] Poly(3-hexylthiophene) (P3HT) is a common choice for this method.[13]

#### Materials:

- Surface-treated Si/SiO<sub>2</sub> substrates

- High-regioregularity P3HT (e.g., >99%)[13]

- Solvent (e.g., chloroform, chlorobenzene, or a mixture)[13]

- Spin-coater

- Hotplate

# Procedure:

- Prepare a solution of P3HT in the chosen solvent. A typical concentration is 5-10 mg/mL.[13] Stir the solution gently for several hours in the dark to ensure complete dissolution.

- Place a surface-treated substrate onto the chuck of the spin-coater.

- Dispense the P3HT solution onto the center of the substrate.

- Spin-coat the solution. A typical two-step program might be:

- 500 RPM for 5 seconds (for spreading).

- 1500-2500 RPM for 30-60 seconds (for thinning).[10][13]

- Transfer the coated substrate to a hotplate and anneal it to remove residual solvent and improve film crystallinity. A typical annealing temperature for P3HT is 100-150 °C for 10-30 minutes, performed in a nitrogen atmosphere.[13]

# **Protocol 4: Electrode Deposition and Device Finalization**

This protocol describes a top-contact, bottom-gate device architecture, where the source and drain electrodes are deposited on top of the semiconductor layer.[14]

#### Materials:

- Substrate with deposited semiconductor film

- Shadow mask with desired channel length (L) and width (W)

- High-vacuum thermal evaporator

- Gold (Au) or other suitable metal for electrodes

#### Procedure:

- Carefully place the shadow mask over the semiconductor film on the substrate. The openings in the mask will define the source and drain electrodes.

- Load the substrate and mask assembly into a high-vacuum thermal evaporator.

- Evacuate the chamber to a pressure of 10<sup>-6</sup> mbar or lower.

- Deposit a 40-50 nm thick layer of gold (Au) through the mask onto the substrate.[13] Gold is often used for p-type semiconductors due to its high work function, which facilitates efficient hole injection.[8]

- Remove the substrate from the evaporator. The OTFT is now ready for characterization.

# Data Presentation: Performance of Thiophene-Based OTFTs

The performance of OTFTs is highly dependent on the specific thiophene derivative, its purity, and the fabrication parameters. The regionegularity of polymers like P3HT is a critical factor; higher regionegularity leads to better molecular packing and improved charge mobility.[13][15] [16]

| Thiophene<br>Compound                                                | Deposition<br>Method  | Mobility<br>(cm²/Vs) | On/Off<br>Ratio   | Substrate/D ielectric              | Reference |

|----------------------------------------------------------------------|-----------------------|----------------------|-------------------|------------------------------------|-----------|

| Poly(3-<br>hexylthiophen<br>e) (P3HT)                                | Spin-Coating          | 0.01 - 0.1           | > 10 <sup>5</sup> | OTS-treated<br>Si/SiO <sub>2</sub> | [1][13]   |

| DHFTTF                                                               | Vacuum<br>Evaporation | up to 0.12           | ~ 105             | Si/SiO2                            | [17]      |

| Thiophene-<br>Anthracene<br>Derivative                               | Vacuum<br>Evaporation | up to 0.50           | > 107             | Si/SiO2                            | [18]      |

| N-decylated<br>triindole-<br>thiophene                               | Spin-Coating          | 5 x 10 <sup>-4</sup> | -                 | OTS-treated<br>Si/SiO <sub>2</sub> | [10]      |

| Dinaphtho[2,<br>3-b:2',3'-<br>f]thieno[3,2-<br>b]thiophene<br>(DNTT) | Vacuum<br>Evaporation | ~1.0                 | > 10 <sup>6</sup> | Cytop                              | [5][7]    |

Note: Performance metrics can vary significantly based on specific processing conditions such as solvent choice, annealing temperature, and electrode material.

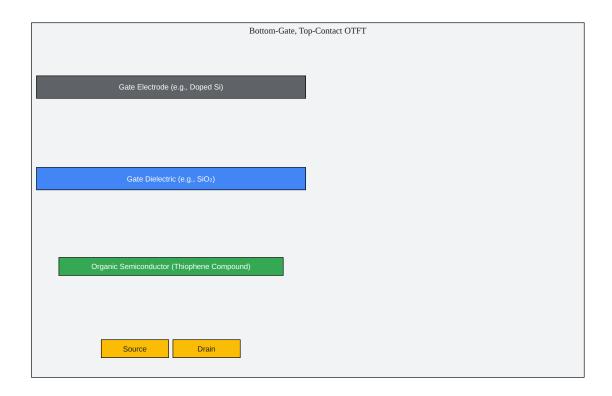

# Visualizations Device Architecture

The most common OTFT architecture is the Bottom-Gate, Top-Contact configuration, where the gate is at the bottom, and the source/drain electrodes are deposited on top of the semiconductor.

Click to download full resolution via product page

Caption: Diagram of a bottom-gate, top-contact OTFT structure.

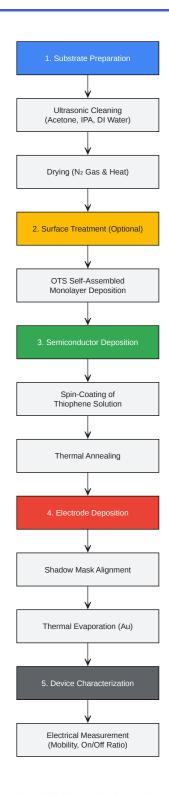

# **Experimental Workflow**

The fabrication of a solution-processed OTFT follows a sequential workflow, from substrate preparation to final device characterization.

Click to download full resolution via product page

Caption: Workflow for solution-processed thiophene OTFT fabrication.

# **Need Custom Synthesis?**

BenchChem offers custom synthesis for rare earth carbides and specific isotopiclabeling.

Email: info@benchchem.com or Request Quote Online.

# References

- 1. Item Fabrication and characterisation of organic thin-film transistors for sensing applications Open Research Newcastle Figshare [openresearch.newcastle.edu.au]

- 2. Thiophene polymer semiconductors for organic thin-film transistors PubMed [pubmed.ncbi.nlm.nih.gov]

- 3. researchgate.net [researchgate.net]

- 4. Oligofluorene-Thiophene Derivatives as High Performance Semiconductors for Organic Thin Film Transistors | Nokia.com [nokia.com]

- 5. Stability of organic thin-film transistors based on ultrathin films of dinaphtho[2,3-b:2',3'-f]thieno[3,2-b]thiophene (DNTT) Journal of Materials Chemistry C (RSC Publishing) [pubs.rsc.org]

- 6. Crystalline structures in organic semiconductors for high-performance OTFT applications [spiedigitallibrary.org]

- 7. researchgate.net [researchgate.net]

- 8. Organic Materials for Thin Film Transistors [sigmaaldrich.com]

- 9. ossila.com [ossila.com]

- 10. mdpi.com [mdpi.com]

- 11. Patterning technology for solution-processed organic crystal field-effect transistors PMC [pmc.ncbi.nlm.nih.gov]

- 12. researchgate.net [researchgate.net]

- 13. Performance evaluation of highly regioregular "P3HT" | TCI AMERICA [tcichemicals.com]

- 14. d31kydh6n6r5j5.cloudfront.net [d31kydh6n6r5j5.cloudfront.net]

- 15. [PDF] Regioregularity effect on the self-assembly behavior of poly(3-hexylthiophene): the significance of triad sequence | Semantic Scholar [semanticscholar.org]

- 16. researchgate.net [researchgate.net]

- 17. pubs.acs.org [pubs.acs.org]

- 18. web.pkusz.edu.cn [web.pkusz.edu.cn]

- To cite this document: BenchChem. [Application Notes & Protocols: Fabrication of Organic Thin-Film Transistors with Thiophene Compounds]. BenchChem, [2025]. [Online PDF].

Available at: [https://www.benchchem.com/product/b098931#fabrication-of-organic-thin-film-transistors-with-thiophene-compounds]

### **Disclaimer & Data Validity:**

The information provided in this document is for Research Use Only (RUO) and is strictly not intended for diagnostic or therapeutic procedures. While BenchChem strives to provide accurate protocols, we make no warranties, express or implied, regarding the fitness of this product for every specific experimental setup.

**Technical Support:** The protocols provided are for reference purposes. Unsure if this reagent suits your experiment? [Contact our Ph.D. Support Team for a compatibility check]

Need Industrial/Bulk Grade? Request Custom Synthesis Quote

# BenchChem

Our mission is to be the trusted global source of essential and advanced chemicals, empowering scientists and researchers to drive progress in science and industry.

### Contact

Address: 3281 E Guasti Rd

Ontario, CA 91761, United States

Phone: (601) 213-4426

Email: info@benchchem.com