# Application Notes: Antimony Doping of Silicon Wafers

Author: BenchChem Technical Support Team. Date: December 2025

| Compound of Interest |                  |           |

|----------------------|------------------|-----------|

| Compound Name:       | Antimony sulfate |           |

| Cat. No.:            | B147869          | Get Quote |

### Introduction

Doping is a fundamental process in semiconductor manufacturing that involves the intentional introduction of impurities into an intrinsic semiconductor to modulate its electrical properties.[1] Antimony (Sb) is a crucial n-type dopant for silicon (Si), meaning it introduces excess electrons, which become the majority charge carriers.[1][2][3] This process is essential for creating n-type regions in various electronic devices, including integrated circuits, power devices, and solar cells.[2][4][5]

Antimony is particularly valued for its small diffusion coefficient, which allows for the creation of sharp, well-controlled doping profiles and buried layers.[1][2] Its diffusion is primarily substitutional, minimizing anomalous effects that can occur with other dopants.[1] While the prompt specified "antimony sulfate," it is important to note that elemental antimony, antimony trioxide (Sb<sub>2</sub>O<sub>3</sub>), or ionized antimony for implantation are the standard sources used in semiconductor fabrication. Antimony sulfate is not a conventional dopant source for this application.

This document outlines the primary methods for antimony doping: Ion Implantation and Diffusion, providing detailed protocols and relevant technical data for research and development professionals.

## **Key Doping Methodologies**

The two predominant techniques for introducing antimony into a silicon lattice are ion implantation and high-temperature diffusion.[6][7]

- Ion Implantation: This modern technique offers precise control over dopant concentration and depth.[6][7] Antimony ions are generated, accelerated to high energies, and embedded directly into the silicon wafer.[6][7][8] This method is highly reproducible and allows for the creation of complex, shallow junctions.[6][8]

- Diffusion: In this process, the silicon wafer is heated to high temperatures in an environment containing the dopant atoms. The antimony atoms then diffuse from the surface into the silicon lattice.[7] This can be achieved from solid, liquid (spin-on), or gaseous sources.[6]

### **Quantitative Data and Material Properties**

Successful process design requires a thorough understanding of antimony's behavior in silicon. The following tables summarize key quantitative data.

Table 1: Solid Solubility of Antimony in Silicon

The solid solubility is the maximum concentration of antimony that can be dissolved in the silicon lattice at a given temperature. Exceeding this limit can lead to the precipitation of antimony, affecting electrical activation.[9]

| Temperature (°C) | Maximum Solubility (atoms/cm³) |  |

|------------------|--------------------------------|--|

| 900              | ~1.0 x 10 <sup>19</sup>        |  |

| 1000             | ~2.5 x 10 <sup>19</sup>        |  |

| 1100             | ~4.5 x 10 <sup>19</sup>        |  |

| 1200             | ~6.0 x 10 <sup>19</sup>        |  |

| 1250             | ~7.0 x 10 <sup>19</sup> [10]   |  |

| 1300             | ~5.3 x 10 <sup>19</sup> [10]   |  |

Table 2: Typical Ion Implantation Parameters for Antimony

Ion implantation parameters directly control the resulting dopant profile. The energy determines the depth, and the dose determines the concentration.

| Parameter        | Typical Range                                                       | Purpose                                                                                  |

|------------------|---------------------------------------------------------------------|------------------------------------------------------------------------------------------|

| Implant Energy   | 2 keV - 200 keV[6][11][12]                                          | Controls the projected range (depth) of the ions. Lower energy for shallower junctions.  |

| Implant Dose     | 1x10 <sup>13</sup> - 1x10 <sup>16</sup> ions/cm <sup>2</sup> [8][9] | Determines the total number of dopant atoms introduced per unit area.                    |

| Wafer Tilt/Twist | 0° - 7°                                                             | Used to minimize ion channeling effects for more uniform profiles.                       |

| Annealing Temp.  | 600°C - 1100°C[11]                                                  | Required post-implant to repair lattice damage and electrically activate the dopants.[8] |

### Table 3: Resulting Electrical Properties

The primary goal of doping is to control the wafer's electrical resistivity.

| Doping Level       | Typical Resistivity (Ω·cm) | Typical Sheet Resistance $(\Omega/sq)$ |

|--------------------|----------------------------|----------------------------------------|

| Lightly Doped      | 1 - 10                     | > 1000                                 |

| Moderately Doped   | 0.1 - 1                    | 100 - 1000                             |

| Heavily Doped (N+) | < 0.02[5][13]              | < 100                                  |

## **Experimental Protocols**

# Protocol 1: N-Type Doping via Antimony Ion Implantation

This protocol describes a standard process for creating a shallow n-type region using lowenergy antimony ion implantation, suitable for ultra-shallow junctions in CMOS devices.[8][11]

- 1. Materials and Equipment:

- Prime-grade P-type Silicon <100> wafers.

- Ion Implanter (Medium-current, capable of Sb<sup>+</sup> ions).

- Rapid Thermal Annealing (RTA) system.

- Wafer cleaning station (SC-1, SC-2 solutions).

- Four-point probe for sheet resistance measurement.

- Secondary Ion Mass Spectrometry (SIMS) for profile analysis (optional).

- 2. Wafer Preparation (Pre-Implantation Clean):

- Perform a standard RCA clean to remove organic and metallic contaminants.

- Finish with a dilute HF dip to remove the native oxide layer immediately before loading into the implanter.

- Dry the wafers using a nitrogen gun.

- 3. Ion Implantation Procedure:

- Load the cleaned wafers into the ion implanter.

- Set the implantation parameters. For an ultra-shallow junction, a typical recipe is:

- Species: Antimony (Sb+)

- Energy: 5 keV[8]

- Dose: 3 x 10<sup>14</sup> ions/cm<sup>2</sup>[8]

- Tilt/Twist: 7°/22° to minimize channeling.

- Execute the implantation recipe. The process is performed under high vacuum.

- 4. Post-Implantation Annealing (Activation):

- Transfer the implanted wafers to the RTA system.

- Perform a spike anneal to activate the dopants and repair crystal damage with minimal diffusion.[8]

- Ambient: Nitrogen (N<sub>2</sub>)

- Temperature: 950°C[8]

- Time: 1-5 seconds (spike).

- Allow the wafers to cool down before removal.

- 5. Characterization:

- Measure the sheet resistance across the wafer using a four-point probe to confirm successful doping and activation.

- (Optional) Analyze the dopant concentration versus depth profile using SIMS.

## Protocol 2: N-Type Doping via Spin-On Dopant (SOD) Diffusion

This protocol details a diffusion process using a liquid antimony source, which is spun onto the wafer. This method is simpler than traditional gas-phase diffusion and suitable for applications where precise junction control is less critical than in ion implantation.[6]

- 1. Materials and Equipment:

- Prime-grade P-type Silicon <100> wafers.

- Antimony-based Spin-On Dopant (SOD) solution.

- · Spin coater.

- Hot plate.

- Diffusion furnace with nitrogen (N<sub>2</sub>) and oxygen (O<sub>2</sub>) gas sources.

- Wafer cleaning station.

- Four-point probe.

- 2. Wafer Preparation:

- Perform a standard RCA clean on the silicon wafers.

- Perform a pre-bake on a hot plate at 150°C for 5 minutes to dehydrate the wafer surface.

- 3. SOD Application and Bake:

- Center a wafer on the spin coater chuck.

- Dispense the antimony SOD solution onto the center of the wafer.

- Spin the wafer at 3000 RPM for 30 seconds to achieve a uniform film.

- Transfer the wafer to a hot plate and perform a soft bake at 200°C for 15 minutes to evaporate the solvent.

- 4. High-Temperature Drive-In Diffusion:

- Load the coated wafers into the diffusion furnace at a standby temperature of ~800°C.

- Ramp the temperature up to the drive-in temperature, typically 1100-1200°C.

- Perform the drive-in step in a controlled ambient:

- Temperature: 1150°C

- Time: 30-60 minutes.

- Ambient: 95% N<sub>2</sub> / 5% O<sub>2</sub>. The small amount of oxygen helps maintain the integrity of the dopant source layer.

- Ramp the temperature down and pull the wafers from the furnace.

- 5. Dopant Glass Removal and Characterization:

- The diffusion process forms a layer of antimony-silicate glass on the surface. Remove this layer by immersing the wafers in a 10:1 buffered oxide etch (BOE) solution for 1-2 minutes.

- Rinse with deionized water and dry with a nitrogen gun.

- Measure the sheet resistance with a four-point probe to determine the final doping level.

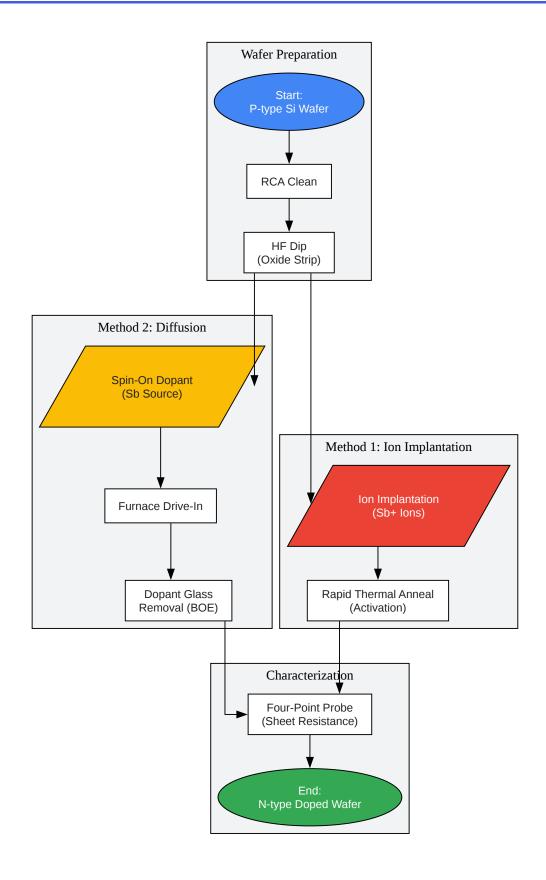

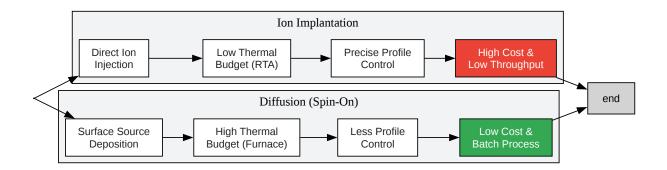

# Visualizations Experimental and Logical Workflows

Click to download full resolution via product page

Caption: Workflow for Antimony Doping of Silicon Wafers.

Click to download full resolution via product page

Caption: Comparison of Implantation vs. Diffusion Doping.

### **Need Custom Synthesis?**

BenchChem offers custom synthesis for rare earth carbides and specific isotopiclabeling.

Email: info@benchchem.com or Request Quote Online.

## References

- 1. Doping (semiconductor) Wikipedia [en.wikipedia.org]

- 2. siliconmaterials.com [siliconmaterials.com]

- 3. sfu.ca [sfu.ca]

- 4. pv-magazine.com [pv-magazine.com]

- 5. powerwaywafer.com [powerwaywafer.com]

- 6. waferpro.com [waferpro.com]

- 7. Doping Methods in Silicon Wafer Processing [waferworld.com]

- 8. US20060017079A1 N-type transistor with antimony-doped ultra shallow source and drain Google Patents [patents.google.com]

- 9. repository.rit.edu [repository.rit.edu]

- 10. Equilibrium Carrier Density and Solubility of Antimony in Silicon for JES IBM Research [research.ibm.com]

- 11. Research Portal [openresearch.surrey.ac.uk]

- 12. researchgate.net [researchgate.net]

- 13. electrochem.org [electrochem.org]

- To cite this document: BenchChem. [Application Notes: Antimony Doping of Silicon Wafers].

BenchChem, [2025]. [Online PDF]. Available at: [https://www.benchchem.com/product/b147869#doping-silicon-wafers-with-antimony-sulfate]

### **Disclaimer & Data Validity:**

The information provided in this document is for Research Use Only (RUO) and is strictly not intended for diagnostic or therapeutic procedures. While BenchChem strives to provide accurate protocols, we make no warranties, express or implied, regarding the fitness of this product for every specific experimental setup.

**Technical Support:**The protocols provided are for reference purposes. Unsure if this reagent suits your experiment? [Contact our Ph.D. Support Team for a compatibility check]

Need Industrial/Bulk Grade? Request Custom Synthesis Quote

## BenchChem

Our mission is to be the trusted global source of essential and advanced chemicals, empowering scientists and researchers to drive progress in science and industry. Contact

Address: 3281 E Guasti Rd

Ontario, CA 91761, United States

Phone: (601) 213-4426

Email: info@benchchem.com