An In-depth Technical Guide to Digital Frequency Display Drivers

Author: BenchChem Technical Support Team. Date: December 2025

| Compound of Interest |           |           |

|----------------------|-----------|-----------|

| Compound Name:       | TD-6301   |           |

| Cat. No.:            | B10826828 | Get Quote |

For Researchers, Scientists, and Drug Development Professionals

This technical guide provides a comprehensive overview of the core principles, architectures, and performance characteristics of digital frequency display drivers. It is intended for researchers, scientists, and drug development professionals who utilize instrumentation where precise frequency measurement and display are critical. This document details the underlying technologies, offers quantitative comparisons of different driver architectures, and provides standardized experimental protocols for their characterization and validation.

## Core Principles of Digital Frequency Display Drivers

A digital frequency display driver is a system responsible for measuring an input signal's frequency and presenting it on a digital display. The fundamental principle of operation for most digital frequency counters involves counting the number of cycles of an input signal within a precisely defined time interval, known as the gate time.[1][2] The accuracy of the frequency measurement is highly dependent on the stability of the internal timebase oscillator that generates this gate time.[2]

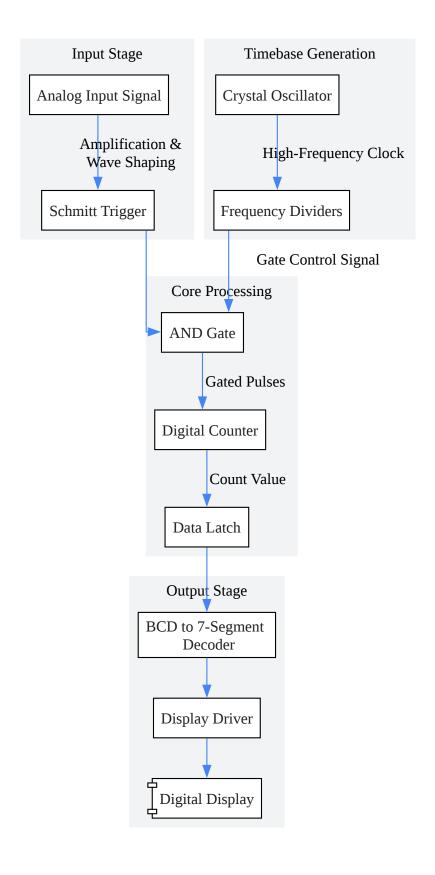

The core process can be broken down into the following stages:

Signal Conditioning: The input signal is typically amplified and converted into a clean square wave with sharp edges that are compatible with digital logic circuits. This is often achieved using a Schmitt trigger.[3][4]

- Gating: The conditioned signal is then passed through a logic gate (typically an AND gate) that is controlled by the timebase. The gate is opened for a precise duration, allowing a specific number of signal cycles to pass through.[5]

- Counting: A digital counter accumulates the number of cycles that pass through the gate.

- Latching and Decoding: At the end of the gate time, the final count is transferred to a latch to hold the value stable. This value is then decoded from its binary or BCD (Binary Coded Decimal) format into a format suitable for the display.[1][6]

- Display Driving: Finally, the decoded information is sent to the display driver, which provides

the necessary voltages and currents to illuminate the segments of the display (e.g., 7segment LED or LCD) to show the frequency.

Two primary counting techniques are employed:

- Direct Counting: This method, as described above, counts the input signal cycles over a fixed gate time. Its resolution is limited, especially for low-frequency signals.

- Reciprocal Counting: This more advanced technique measures the period of the input signal

by counting cycles of a high-frequency reference clock during one or more periods of the

input signal. The frequency is then calculated as the reciprocal of the measured period (F =

1/T).[7] This method provides high resolution for both high and low-frequency signals.

# Architectural Approaches to Digital Frequency Display Drivers

Digital frequency display drivers can be implemented using several distinct architectural approaches, each with its own set of trade-offs in terms of performance, complexity, and cost.

## **Discrete Logic IC-Based Drivers**

This traditional approach utilizes standard logic integrated circuits (ICs) such as counters, latches, and decoders.

Core Components:

- Counters: Typically BCD (Binary Coded Decimal) counters like the 74HC390 or CD4033 are used.[3][7][8][9][10][11][12] The CD4033 is a Johnson decade counter with an integrated 7-segment decoder.[3][9]

- Display Driver/Decoder: If the counter does not have an integrated decoder, a separate

BCD-to-7-segment decoder/driver IC is required.

- Timebase: A crystal oscillator combined with divider circuits generates the precise gate time.

This approach is well-suited for educational purposes and applications where the design requirements are fixed and high-speed performance is not the primary concern.

#### **Microcontroller-Based Drivers**

Microcontrollers (MCUs) offer a flexible and compact solution for frequency counting by implementing the core logic in software.

- Core Components:

- Microcontroller: Popular choices include the PIC family (e.g., PIC16F84) and the 8051 architecture.[13][14][15][16][17]

- Internal Timers/Counters: The MCU's built-in hardware timers are used to count the input signal cycles and to generate the gate time.[13][18]

- Display: The MCU directly drives an LCD or LED display.

Microcontroller-based designs are highly versatile, allowing for features like auto-ranging, offset calculations, and various display modes to be implemented in software.[15][17]

### **FPGA-Based Drivers**

Field-Programmable Gate Arrays (FPGAs) provide the highest performance and flexibility by allowing for the implementation of custom digital logic in hardware.

Core Components:

- FPGA: A configurable fabric of logic blocks that can be programmed using a Hardware

Description Language (HDL) such as VHDL or Verilog.[1][4]

- HDL Code: The counting, gating, and control logic are all defined in the HDL code.[2][19]

[20]

- High-Speed I/O: FPGAs can handle very high-frequency input signals.

FPGA-based drivers are ideal for high-performance applications requiring low latency, high precision, and the ability to perform parallel signal processing.[1][8][9]

# **Quantitative Data and Performance Comparison**

The choice of architecture significantly impacts the performance of the digital frequency display driver. The following tables summarize key quantitative data for representative components and compare the different architectural approaches.

| Parameter            | 74HC390 (Counter)                | CD4033<br>(Counter/Decoder)                  | ICM7226A<br>(Universal Counter)                             |

|----------------------|----------------------------------|----------------------------------------------|-------------------------------------------------------------|

| Technology           | High-speed Si-gate<br>CMOS       | CMOS                                         | CMOS                                                        |

| Max. Clock Frequency | 36 MHz (typical at 5V)           | 6 MHz (typical at 10V)                       | 10 MHz                                                      |

| Supply Voltage Range | 2.0V to 6.0V                     | 3V to 18V                                    | 4.0V to 6.0V                                                |

| Key Features         | Dual 4-bit decade ripple counter | Decade counter with 7-segment decoded output | Fully integrated<br>universal counter and<br>display driver |

| Datasheet            | [7][8][10][11][12]               | [3][5][9][21][22]                            | [19][23][24][25][26]                                        |

| Parameter                   | PIC16F84A (MCU)                      | AT89S52 (8051<br>MCU)                | FPGA (Generic)                                    |

|-----------------------------|--------------------------------------|--------------------------------------|---------------------------------------------------|

| Max. Operating Frequency    | 20 MHz                               | 33 MHz                               | >500 MHz (depends<br>on FPGA family)              |

| Internal<br>Timers/Counters | 1 x 8-bit                            | 3 x 16-bit                           | Implemented in logic                              |

| Power Consumption           | Low                                  | Low to Moderate                      | Moderate to High (application dependent)          |

| Flexibility                 | High (Software-<br>defined features) | High (Software-<br>defined features) | Very High (Hardware-<br>defined architecture)     |

| Development<br>Complexity   | Moderate                             | Moderate                             | High                                              |

| Key Features                | Cost-effective, wide availability    | Large instruction set, ample I/O     | Parallel processing,<br>high-speed<br>performance |

| References                  | [14][15][16][17]                     | [13][18][27]                         | [1][4][28]                                        |

## **Experimental Protocols**

To ensure the accuracy and reliability of a digital frequency display driver, a series of characterization experiments should be performed. The following are detailed methodologies for key performance tests.

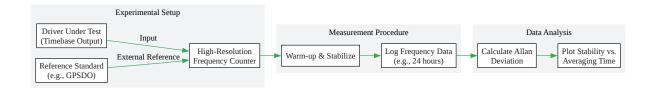

## **Experiment 1: Timebase Stability Measurement**

Objective: To determine the short-term and long-term stability of the driver's internal timebase oscillator.

#### Equipment:

Digital Frequency Display Driver under test

- High-stability reference frequency standard (e.g., GPS-disciplined oscillator (GPSDO) or Rubidium standard) with NIST traceability.[14][21][29]

- · High-resolution frequency counter

- Environmental chamber (for temperature stability testing)

- Data logging software

#### Procedure:

- Connect the timebase output of the driver under test to the input of the high-resolution frequency counter.

- Connect the external reference from the GPSDO or Rubidium standard to the external reference input of the frequency counter.

- Allow the driver and the reference standard to warm up and stabilize for the manufacturerspecified time (typically at least 30 minutes).[29][30]

- Configure the data logging software to record the frequency measurement from the counter at regular intervals (e.g., every second) for an extended period (e.g., 24 hours).

- For temperature stability, place the driver under test inside the environmental chamber and repeat the measurement at different temperature points across its specified operating range.

- Analyze the collected data to calculate key stability metrics such as Allan deviation.

## **Experiment 2: Input Sensitivity Determination**

Objective: To determine the minimum input signal amplitude required for reliable frequency counting across the specified frequency range.

#### Equipment:

- Digital Frequency Display Driver under test

- Signal generator

- · High-precision attenuator

- Oscilloscope

- Power splitter

#### Procedure:

- Connect the signal generator output to the input of the power splitter.

- Connect one output of the power splitter to the input of the driver under test.

- Connect the other output of the power splitter to the oscilloscope to monitor the true signal amplitude.

- Set the signal generator to a specific frequency within the driver's operating range.

- Start with a signal amplitude well above the expected sensitivity level.

- Gradually decrease the signal amplitude using the high-precision attenuator until the frequency reading on the driver becomes unstable or erroneous.

- Record the minimum stable amplitude from the oscilloscope.

- Repeat this procedure for multiple frequency points across the driver's specified range.[18]

## **Experiment 3: Jitter Characterization**

Objective: To measure the timing jitter of the digital frequency display driver's internal processes.

#### Equipment:

- Digital Frequency Display Driver under test

- High-bandwidth oscilloscope with jitter analysis software

- Low-jitter signal source

#### Procedure:

- Connect the low-jitter signal source to the input of the driver.

- Probe the internal nodes of the driver, such as the output of the signal conditioning circuit and the clock signals, using the high-bandwidth oscilloscope.

- Use the oscilloscope's jitter analysis software to measure various jitter parameters, including period jitter, cycle-to-cycle jitter, and Time Interval Error (TIE).[22][25][31][32]

- Analyze the jitter histograms and spectra to identify the sources and characteristics of the jitter.[22][25][32]

# Visualizations Signaling Pathways and Workflows

Click to download full resolution via product page

Caption: General signaling pathway for a direct-counting digital frequency display driver.

#### Click to download full resolution via product page

Caption: Experimental workflow for measuring timebase stability.

#### Click to download full resolution via product page

Caption: Logical relationship between driver architecture and key performance metrics.

#### **Need Custom Synthesis?**

BenchChem offers custom synthesis for rare earth carbides and specific isotopiclabeling.

Email: info@benchchem.com or Request Quote Online.

## References

- 1. wevolver.com [wevolver.com]

- 2. secs.oakland.edu [secs.oakland.edu]

- 3. fscircuits.com [fscircuits.com]

- 4. researchgate.net [researchgate.net]

- 5. leapsecond.com [leapsecond.com]

- 6. febo.com [febo.com]

- 7. Frequency Counter: Block Diagram, Circuit, Types and Its Applications [elprocus.com]

- 8. logic-fruit.com [logic-fruit.com]

- 9. flexiblepcbboard.com [flexiblepcbboard.com]

- 10. pendulum-instruments.com [pendulum-instruments.com]

- 11. apps.dtic.mil [apps.dtic.mil]

- 12. Frequency Counter: Blog Diagram, Circuit, Types, Applications [tescaglobal.com]

- 13. High Resolution Frequency Counter: 5 Steps (with Pictures) Instructables [instructables.com]

- 14. tf.nist.gov [tf.nist.gov]

- 15. Trusted & Reliable Frequency Counter Calibration ISO 17025 Certified [prismcalibration.com]

- 16. tf.nist.gov [tf.nist.gov]

- 17. Frequency Counter Specifications » Electronics Notes [electronics-notes.com]

- 18. VHDL Counter · GitHub [gist.github.com]

- 19. VHDL Code for Clock Divider (Frequency Divider) [allaboutfpga.com]

- 20. Frequency Measurement Guidelines for Oscillators | SiTime [sitime.com]

- 21. youtube.com [youtube.com]

- 22. community.infineon.com [community.infineon.com]

- 23. jakelectronics.com [jakelectronics.com]

- 24. picture.iczhiku.com [picture.iczhiku.com]

- 25. 82.65.153.34 [82.65.153.34]

- 26. quora.com [quora.com]

- 27. fenix.tecnico.ulisboa.pt [fenix.tecnico.ulisboa.pt]

- 28. emlcalibration.com [emlcalibration.com]

- 29. keysight.com [keysight.com]

- 30. anlage.umd.edu [anlage.umd.edu]

- 31. atlantis-press.com [atlantis-press.com]

- 32. You are being redirected... [sjelectronics.co.uk]

- To cite this document: BenchChem. [An In-depth Technical Guide to Digital Frequency Display Drivers]. BenchChem, [2025]. [Online PDF]. Available at: [https://www.benchchem.com/product/b10826828#introduction-to-digital-frequency-display-drivers]

#### **Disclaimer & Data Validity:**

The information provided in this document is for Research Use Only (RUO) and is strictly not intended for diagnostic or therapeutic procedures. While BenchChem strives to provide accurate protocols, we make no warranties, express or implied, regarding the fitness of this product for every specific experimental setup.

**Technical Support:** The protocols provided are for reference purposes. Unsure if this reagent suits your experiment? [Contact our Ph.D. Support Team for a compatibility check]

Need Industrial/Bulk Grade? Request Custom Synthesis Quote

## BenchChem

Our mission is to be the trusted global source of essential and advanced chemicals, empowering scientists and researchers to drive progress in science and industry. Contact

Address: 3281 E Guasti Rd

Ontario, CA 91761, United States

Phone: (601) 213-4426

Email: info@benchchem.com