# A Researcher's Guide to CPU Models in gem5: Atomic, Timing, and O3

Author: BenchChem Technical Support Team. Date: December 2025

An In-depth Technical Guide for Scientists and Drug Development Professionals

The gem5 simulator is a powerful and flexible tool for computer architecture research, offering a variety of CPU models to suit different research needs. For researchers, scientists, and drug development professionals leveraging simulation in their work, understanding the trade-offs between these models is crucial for obtaining accurate and timely results. This guide provides an in-depth technical exploration of three core CPU models in gem5: AtomicSimpleCPU, TimingSimpleCPU, and the detailed Out-of-Order (O3) CPU. We will delve into their architectures, use cases, and performance characteristics, providing detailed experimental protocols and comparative data to inform your simulation choices.

# **Introduction to gem5 CPU Models**

The gem5 simulator's modular design allows for the interchange of various components, with the CPU model being one of the most critical choices, directly impacting simulation speed and accuracy. The selection of a CPU model should align with the specific research question. For instance, early-stage functional validation might prioritize speed over cycle-level accuracy, while detailed microarchitectural studies demand a more precise, albeit slower, model.

gem5 offers several CPU models, but this guide focuses on three fundamental types that represent a spectrum of trade-offs:

AtomicSimpleCPU: A simple, in-order CPU model designed for the fastest possible functional simulation.[1]

- TimingSimpleCPU: An in-order CPU model that introduces timing to memory accesses,

offering a balance between speed and accuracy.[1]

- O3CPU (Out-of-Order CPU): A detailed, superscalar, out-of-order processor model for high-fidelity microarchitectural exploration.

Simulations in gem5 can be run in two primary modes:

- System-Call Emulation (SE) Mode: In this mode, gem5 simulates the CPU and memory system, trapping and emulating system calls made by the application to the host operating system. SE mode is generally faster and easier to configure.[3]

- Full System (FS) Mode: FS mode simulates a complete hardware system, allowing an unmodified operating system to boot and run. This mode is more realistic, especially for studies where OS interactions are significant, but it is also more complex to set up and slower to simulate.[4]

# A Deep Dive into gem5 CPU Models AtomicSimpleCPU: The Speed Runner

The AtomicSimpleCPU is a functionally-first, in-order CPU model.[1] Its primary design goal is simulation speed. It achieves this by treating memory accesses as "atomic," meaning they complete in a single, variable-latency step without modeling the detailed contention and queuing delays of the memory system.[5] While it receives a latency from the memory system, the CPU itself does not stall; it can proceed with subsequent instructions, making it a non-cycle-accurate model.

#### Key Characteristics:

- Execution Model: In-order, single-cycle instruction execution (except for memory accesses).

- Memory Model: Atomic memory accesses. The simulation proceeds without waiting for memory responses, though a timing annotation is received.

- Use Cases: Ideal for fast-forwarding to a region of interest in a simulation, functional verification of code, and studies where detailed cycle-level accuracy of the CPU core is not the primary concern.

Limitations: Not suitable for performance analysis that depends on accurate timing of CPU pipeline effects or memory system interactions.

## **TimingSimpleCPU: A Step Towards Realism**

The TimingSimpleCPU builds upon the simplicity of the AtomicSimpleCPU by introducing a more realistic memory timing model.[1] Like its atomic counterpart, it is an in-order model. However, when a memory access is initiated, the CPU stalls and waits for a response from the memory system, accurately modeling memory access latencies.[5] This makes it more cycle-accurate than the AtomicSimpleCPU, particularly for memory-bound workloads.

#### Key Characteristics:

- Execution Model: In-order, single-cycle instruction execution, but with stalls on memory accesses.

- Memory Model: Timing-based memory accesses. The CPU waits for the memory system to respond before proceeding.

- Use Cases: Suitable for studies where the performance of the memory subsystem is a key factor, but a full out-of-order core model is not necessary. It offers a good balance between simulation speed and memory-related performance accuracy.

- Limitations: As an in-order model, it does not capture the complexities of modern superscalar, out-of-order processors, such as instruction-level parallelism.

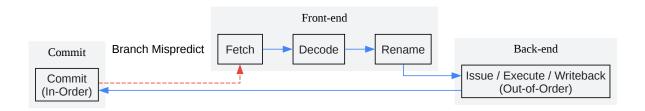

#### O3CPU: The Pinnacle of Detail

The O3CPU is gem5's most detailed and complex CPU model, implementing a superscalar, out-of-order execution pipeline loosely based on the Alpha 21264.[2] It models the key components of a modern high-performance CPU, including a reorder buffer (ROB), issue queues, and physical register files, enabling it to exploit instruction-level parallelism.[6] The O3CPU uses a timing-based memory model, similar to the TimingSimpleCPU.

#### Pipeline Stages:

The O3CPU implements a configurable pipeline, with the following key stages[2][7]:

- Fetch: Fetches instructions from the instruction cache.

- Decode: Decodes instructions into micro-operations.

- Rename: Renames architectural registers to physical registers to eliminate false dependencies.

- Issue/Execute/Writeback (IEW): Dispatches instructions to functional units, executes them, and writes back the results.

- Commit: Commits instructions in-order, making their results architecturally visible.

#### Key Characteristics:

- Execution Model: Out-of-order, superscalar pipeline.

- Memory Model: Timing-based memory accesses.

- Use Cases: The preferred model for detailed microarchitectural studies, including research on instruction scheduling, branch prediction, cache coherence protocols, and other performance-critical aspects of modern CPUs.

- Limitations: The high level of detail makes it the slowest of the three models. Its complexity

also presents a steeper learning curve for configuration and analysis.

# **Quantitative Performance Comparison**

To illustrate the performance trade-offs between the CPU models, the following table summarizes typical results for simulation speed and simulated performance across a selection of benchmarks. The data presented here is illustrative and based on trends observed in various studies. Actual results will vary based on the specific benchmark, system configuration, and host machine.

| CPU Model       | Simulation Speed<br>(Instructions/Secon<br>d) | Simulated<br>Performance (IPC) | Cycles Per<br>Instruction (CPI) |

|-----------------|-----------------------------------------------|--------------------------------|---------------------------------|

| AtomicSimpleCPU | Very High (e.g., > 1<br>MIPS)                 | High (often unrealistic)       | Low (often unrealistic)         |

| TimingSimpleCPU | Moderate (e.g., 100-<br>500 KIPS)             | Moderate                       | Moderate                        |

| O3CPU           | Low (e.g., 10-100<br>KIPS)                    | Realistic                      | Realistic                       |

Table 1: Illustrative Performance Comparison of gem5 CPU Models.

## **O3CPU Microarchitectural Parameters**

The O3CPU model is highly configurable, allowing researchers to model a wide range of out-of-order processor designs. The table below lists some of the key parameters that can be adjusted in the gem5 configuration scripts.

| Parameter        | Description                                                  | Default Value (Typical) |

|------------------|--------------------------------------------------------------|-------------------------|

| fetchWidth       | Number of instructions fetched per cycle.                    | 8                       |

| decodeWidth      | Number of instructions decoded per cycle.                    | 8                       |

| renameWidth      | Number of instructions renamed per cycle.                    | 8                       |

| issueWidth       | Number of instructions issued to functional units per cycle. | 8                       |

| commitWidth      | Number of instructions committed per cycle.                  | 8                       |

| numROBEntries    | Number of entries in the Reorder Buffer.                     | 192                     |

| numIQEntries     | Number of entries in the Instruction Queue (Issue Queue).    | 64                      |

| numPhysIntRegs   | Number of physical integer registers.                        | 256                     |

| numPhysFloatRegs | Number of physical floating-<br>point registers.             | 256                     |

| branchPred       | The branch predictor to use (e.g., TournamentBP).            | TournamentBP            |

Table 2: Key Microarchitectural Parameters of the O3CPU Model.

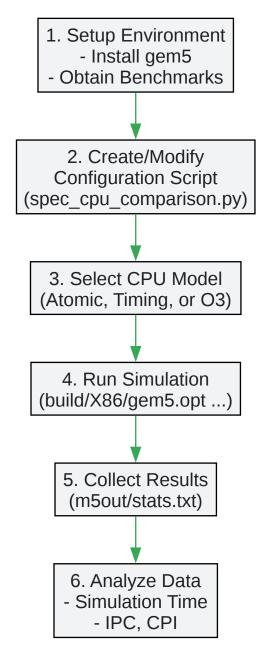

# **Experimental Protocols**

This section provides a detailed methodology for conducting a comparative study of the three CPU models in gem5 using the SPEC CPU® 2017 benchmark suite in Full System (FS) mode. This protocol is based on established practices for running SPEC benchmarks in gem5.[4]

## **Prerequisites**

- gem5 Installation: A working installation of gem5, compiled for the desired instruction set architecture (e.g., X86 or ARM).

- SPEC CPU 2017 Benchmark Suite: A licensed copy of the SPEC CPU 2017 benchmark suite.

- Disk Image and Kernel: A pre-compiled disk image containing the SPEC benchmarks and a compatible Linux kernel. Resources for creating these are available through the gem5 project.

## **Configuration Script**

The following Python script (spec\_cpu\_comparison.py) provides a basic framework for running a SPEC benchmark with a chosen CPU model.

# **Running the Simulation**

- Compile the Configuration: Ensure the Python script is in a directory accessible by gem5.

- Execute the Simulation: Run the simulation from the gem5 directory using the following command structure. The --cpu-type flag in the configuration script will determine which CPU model is used.

- Collect and Analyze Results: After the simulation completes, the statistics will be available in the m5out/stats.txt file. Key metrics to analyze include sim\_seconds (simulation time), system.cpu.ipc (Instructions Per Cycle), and system.cpu.cpi (Cycles Per Instruction).

# **Visualizing CPU Model Workflows**

The following diagrams, generated using the DOT language, illustrate the logical workflows of the AtomicSimpleCPU, TimingSimpleCPU, and O3CPU models, as well as the experimental workflow.

# **AtomicSimpleCPU Workflow**

Click to download full resolution via product page

AtomicSimpleCPU instruction processing flow.

# **TimingSimpleCPU Workflow**

Click to download full resolution via product page

TimingSimpleCPU instruction processing flow with memory stall.

## **O3CPU Pipeline Workflow**

Click to download full resolution via product page

High-level pipeline stages of the O3CPU model.

### **Experimental Workflow**

Click to download full resolution via product page

Workflow for comparing CPU models in gem5.

## Conclusion

Choosing the right CPU model in gem5 is a critical decision that balances simulation speed and accuracy. The AtomicSimpleCPU offers the fastest simulation times, making it ideal for

functional verification and rapid exploration. The TimingSimpleCPU provides a middle ground by incorporating realistic memory timing, suitable for studies where memory performance is key. For the highest fidelity and detailed microarchitectural analysis, the O3CPU is the model of choice, despite its slower simulation speed.

For researchers, scientists, and drug development professionals, this guide provides the foundational knowledge to make informed decisions about which CPU model best suits their research objectives. By understanding the architectural nuances, performance trade-offs, and experimental methodologies, you can effectively leverage the power of gem5 for your computational research.

#### **Need Custom Synthesis?**

BenchChem offers custom synthesis for rare earth carbides and specific isotopiclabeling.

Email: info@benchchem.com or Request Quote Online.

### References

- 1. gem5: Simple CPU Models [gem5.org]

- 2. gem5: Out of order CPU model [gem5.org]

- 3. gem5: Creating a simple configuration script [gem5.org]

- 4. gem5: SPEC Tutorial [gem5.org]

- 5. ws.engr.illinois.edu [ws.engr.illinois.edu]

- 6. gem5: More complex configuration script [courses.grainger.illinois.edu]

- 7. O3CPU gem5 [old.gem5.org]

- To cite this document: BenchChem. [A Researcher's Guide to CPU Models in gem5: Atomic, Timing, and O3]. BenchChem, [2025]. [Online PDF]. Available at: [https://www.benchchem.com/product/b12410503#exploring-different-cpu-models-in-gem-5-e-g-atomic-timing-o3]

#### **Disclaimer & Data Validity:**

The information provided in this document is for Research Use Only (RUO) and is strictly not intended for diagnostic or therapeutic procedures. While BenchChem strives to provide accurate protocols, we make no warranties, express or implied, regarding the fitness of this product for every specific experimental setup.

**Technical Support:**The protocols provided are for reference purposes. Unsure if this reagent suits your experiment? [Contact our Ph.D. Support Team for a compatibility check]

Need Industrial/Bulk Grade? Request Custom Synthesis Quote

# BenchChem

Our mission is to be the trusted global source of essential and advanced chemicals, empowering scientists and researchers to drive progress in science and industry.

#### Contact

Address: 3281 E Guasti Rd

Ontario, CA 91761, United States

Phone: (601) 213-4426

Email: info@benchchem.com