# A Comparative Guide to the Synthesis of Silicon Nanowires: VLS/CVD vs. MACE

Author: BenchChem Technical Support Team. Date: December 2025

| Compound of Interest |          |           |

|----------------------|----------|-----------|

| Compound Name:       | Silicon  |           |

| Cat. No.:            | B1239273 | Get Quote |

The synthesis of **silicon** nanowires (SiNWs) is a cornerstone of nanoscale research and development, with applications spanning from electronics and photonics to energy storage and biomedical sensing. For researchers, scientists, and drug development professionals, the choice of synthesis method is critical as it dictates the morphology, purity, and ultimately the performance of the resulting nanowires. This guide provides a detailed comparison of two of the most prevalent synthesis techniques: Vapor-Liquid-Solid (VLS) growth, typically conducted via Chemical Vapor Deposition (CVD), and Metal-Assisted Chemical Etching (MACE).

At a Glance: VLS/CVD vs. MACE

| Feature               | Vapor-Liquid-Solid (VLS)<br>via CVD                  | Metal-Assisted Chemical<br>Etching (MACE)                    |

|-----------------------|------------------------------------------------------|--------------------------------------------------------------|

| Principle             | Catalytic growth from a liquid alloy                 | Anisotropic wet etching of a silicon wafer                   |

| Typical Catalyst      | Gold (Au), Copper (Cu)                               | Silver (Ag), Gold (Au),<br>Platinum (Pt)                     |

| Operating Temperature | High (typically >363°C for Au-<br>Si eutectic)[1][2] | Room temperature[2]                                          |

| Cost & Complexity     | Higher cost, more complex equipment (CVD furnace)[3] | Lower cost, simpler setup[4][5]                              |

| Throughput            | Lower, batch-based process                           | High, suitable for large-scale production[6]                 |

| Control over Diameter | Good, determined by catalyst nanoparticle size[1]    | Dependent on metal nanoparticle deposition or lithography[6] |

| Crystallinity         | High, typically single-<br>crystalline[7]            | Crystalline, inherits from the parent wafer[6]               |

| Surface Roughness     | Generally smooth                                     | Can be higher, leading to increased surface defects[8]       |

# **Quantitative Performance Comparison**

The choice of synthesis method significantly impacts the physical and electrical properties of the resulting **silicon** nanowires. The following table summarizes key quantitative parameters for SiNWs produced by VLS/CVD and MACE.

| Parameter         | VLS/CVD                                                                                                                                          | MACE                                                                                                                            |

|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|

| Typical Diameter  | 2.8 nm - 100s of nm[1][8]                                                                                                                        | 55 nm - 140 nm (can be controlled by lithography)[9] [10]                                                                       |

| Typical Length    | Micrometers[11]                                                                                                                                  | Micrometers, with high aspect ratios achievable[10]                                                                             |

| Growth/Etch Rate  | 10 <sup>-2</sup> to 10 <sup>3</sup> nm/min[12]                                                                                                   | Can be high, e.g., ~48.3 nm/s, and is tunable by etchant composition[13]                                                        |

| Typical Density   | Up to 1.1 x 10 <sup>10</sup> cm <sup>-2</sup> [8]                                                                                                | High, can reach ~10 <sup>12</sup><br>NWs/cm²[10]                                                                                |

| Electron Mobility | Generally higher due to<br>smoother surfaces and high<br>crystallinity.[14] Surface<br>roughness is a key factor in<br>mobility degradation.[14] | Can be lower due to increased surface roughness and potential for defects, which act as scattering centers for charge carriers. |

## **Experimental Protocols**

Detailed and reproducible experimental protocols are crucial for the successful synthesis of **silicon** nanowires. Below are representative protocols for both the VLS/CVD and MACE methods.

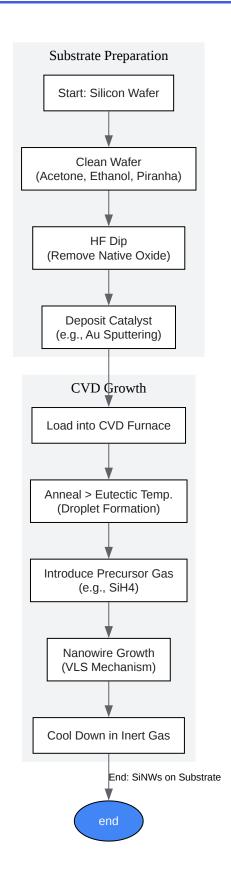

# Vapor-Liquid-Solid (VLS) Synthesis via Chemical Vapor Deposition (CVD)

This protocol describes a typical process for growing **silicon** nanowires on a **silicon** substrate using a gold catalyst.

Materials and Equipment:

- Silicon (100) or (111) wafers

- Gold (Au) sputtering or evaporation system

- Chemical Vapor Deposition (CVD) furnace with gas flow controllers

- Silane (SiH<sub>4</sub>) or Dichlorosilane (SiH<sub>2</sub>Cl<sub>2</sub>) gas

- Inert carrier gas (e.g., Argon, Nitrogen)

- Hydrofluoric acid (HF) solution (for native oxide removal)

- Piranha solution (H<sub>2</sub>SO<sub>4</sub>:H<sub>2</sub>O<sub>2</sub> mixture) for cleaning (use with extreme caution)

#### Procedure:

- Substrate Cleaning: The silicon wafer is first cleaned to remove organic contaminants. This

can be done by sonicating in acetone and ethanol, followed by a piranha etch (e.g., 4:1

H<sub>2</sub>SO<sub>4</sub>:H<sub>2</sub>O<sub>2</sub>) to remove residual organics.

- Native Oxide Removal: Immediately before catalyst deposition, the native oxide layer on the silicon wafer is removed by dipping it in a dilute HF solution (e.g., 2% HF in deionized water) for 1-2 minutes, followed by rinsing with deionized water and drying with nitrogen gas.

- Catalyst Deposition: A thin film of gold (typically 1-10 nm) is deposited onto the cleaned

silicon substrate using sputtering or thermal evaporation.[1]

- Catalyst Annealing and Droplet Formation: The substrate is loaded into the CVD furnace. The furnace is heated to a temperature above the Au-Si eutectic point (363°C) under an inert gas flow.[2] This causes the gold film to form liquid alloy droplets on the **silicon** surface.

- Nanowire Growth: Once the desired temperature is reached and stabilized, the silicon precursor gas (e.g., a mixture of SiH<sub>4</sub> and an inert gas) is introduced into the reaction chamber. The silane decomposes on the surface of the liquid catalyst droplets.

- Supersaturation and Precipitation: As more silicon dissolves into the catalyst droplets, they

become supersaturated. This leads to the precipitation of silicon at the liquid-solid interface,

resulting in the growth of a silicon nanowire.

- Termination and Cooling: After the desired growth time, the precursor gas flow is stopped, and the furnace is cooled down to room temperature under an inert gas flow.

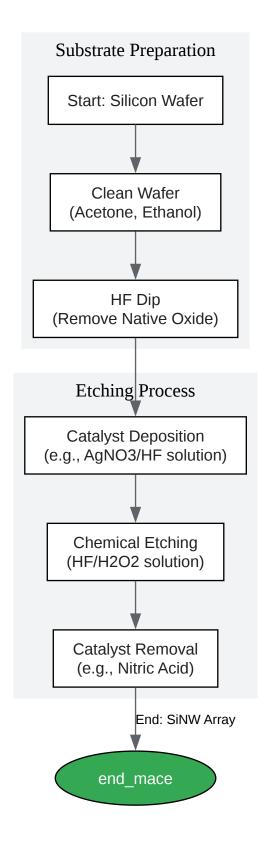

### **Metal-Assisted Chemical Etching (MACE)**

This protocol outlines a common two-step MACE process for fabricating **silicon** nanowire arrays using a silver catalyst.

#### Materials and Equipment:

- Silicon (100) wafers (p-type or n-type)

- Silver nitrate (AgNO₃) solution

- · Hydrofluoric acid (HF) solution

- Hydrogen peroxide (H<sub>2</sub>O<sub>2</sub>) solution

- Nitric acid (HNO<sub>3</sub>) solution (for catalyst removal)

- Beakers and etching containers

- Tweezers

#### Procedure:

- Substrate Cleaning: The silicon wafer is cleaned to remove organic contaminants by sonicating in acetone and ethanol, followed by rinsing with deionized water and drying.

- Native Oxide Removal: The native oxide layer is removed by immersing the wafer in a dilute HF solution (e.g., 5% HF) for 1-2 minutes.

- Catalyst Deposition (Step 1): The cleaned wafer is immersed in an aqueous solution containing silver nitrate (AgNO₃) and hydrofluoric acid (e.g., 0.005 M AgNO₃ and 4.6 M HF) for a short duration (e.g., 10 seconds).[6] This results in the electroless deposition of silver nanoparticles onto the silicon surface. The wafer is then rinsed with deionized water and dried.

- Etching (Step 2): The wafer with the deposited silver nanoparticles is then immersed in an etching solution containing hydrofluoric acid and an oxidizing agent, typically hydrogen peroxide (e.g., 4.6 M HF and 0.3 M H<sub>2</sub>O<sub>2</sub>).[6] The etching process is typically carried out at

room temperature for a desired duration (e.g., 10 minutes) to achieve the target nanowire length.[6]

• Catalyst Removal: After etching, the silver catalyst is removed by immersing the wafer in a nitric acid solution (e.g., 70% HNO₃) for several minutes, followed by thorough rinsing with deionized water and drying.[12]

## **Visualizing the Synthesis Workflows**

The following diagrams, generated using the DOT language, illustrate the experimental workflows for the VLS/CVD and MACE synthesis methods.

Click to download full resolution via product page

VLS/CVD Synthesis Workflow

Click to download full resolution via product page

MACE Synthesis Workflow

In conclusion, both VLS/CVD and MACE are powerful techniques for the synthesis of **silicon** nanowires, each with its own set of advantages and disadvantages. The VLS/CVD method offers precise control and yields high-quality, single-crystalline nanowires, making it suitable for applications where pristine material properties are paramount. In contrast, MACE provides a low-cost, scalable, and high-throughput alternative, which is advantageous for large-area applications such as in photovoltaics and sensing arrays. The choice of synthesis method will ultimately depend on the specific requirements of the intended application, including desired nanowire characteristics, cost considerations, and scalability.

#### **Need Custom Synthesis?**

BenchChem offers custom synthesis for rare earth carbides and specific isotopiclabeling.

Email: info@benchchem.com or Request Quote Online.

### References

- 1. Effect of etching parameters on the electrochemical response of silicon nanowires [publica.fraunhofer.de]

- 2. Silicon Nanowires Synthesis by Metal-Assisted Chemical Etching: A Review PMC [pmc.ncbi.nlm.nih.gov]

- 3. hocityu.com [hocityu.com]

- 4. researchgate.net [researchgate.net]

- 5. pubs.acs.org [pubs.acs.org]

- 6. researchgate.net [researchgate.net]

- 7. Study of the morphological, optical, structural and electrical properties of silicon nanowires at varying concentrations of the catalyst precursor - Materials Advances (RSC Publishing) [pubs.rsc.org]

- 8. nanowires.berkeley.edu [nanowires.berkeley.edu]

- 9. researchgate.net [researchgate.net]

- 10. Significant enhancement of hole mobility in [110] silicon nanowires compared to electrons and bulk silicon PubMed [pubmed.ncbi.nlm.nih.gov]

- 11. Surface roughness induced electron mobility degradation in InAs nanowires PubMed [pubmed.ncbi.nlm.nih.gov]

- 12. researchgate.net [researchgate.net]

- 13. minds.wisconsin.edu [minds.wisconsin.edu]

- 14. researchgate.net [researchgate.net]

- To cite this document: BenchChem. [A Comparative Guide to the Synthesis of Silicon Nanowires: VLS/CVD vs. MACE]. BenchChem, [2025]. [Online PDF]. Available at: [https://www.benchchem.com/product/b1239273#comparing-the-efficacy-of-different-synthesis-methods-for-silicon-nanowires]

#### **Disclaimer & Data Validity:**

The information provided in this document is for Research Use Only (RUO) and is strictly not intended for diagnostic or therapeutic procedures. While BenchChem strives to provide accurate protocols, we make no warranties, express or implied, regarding the fitness of this product for every specific experimental setup.

**Technical Support:** The protocols provided are for reference purposes. Unsure if this reagent suits your experiment? [Contact our Ph.D. Support Team for a compatibility check]

Need Industrial/Bulk Grade? Request Custom Synthesis Quote

## BenchChem

Our mission is to be the trusted global source of essential and advanced chemicals, empowering scientists and researchers to drive progress in science and industry. Contact

Address: 3281 E Guasti Rd

Ontario, CA 91761, United States

Phone: (601) 213-4426

Email: info@benchchem.com