# A Comparative Guide to MOS Capacitors with TEMAZr-Deposited Zirconia Dielectrics

Author: BenchChem Technical Support Team. Date: December 2025

For Researchers, Scientists, and Drug Development Professionals

This guide provides an objective comparison of the electrical characteristics of Metal-Oxide-Semiconductor (MOS) capacitors fabricated with Zirconia (ZrO<sub>2</sub>) dielectrics deposited via the **Tetrakis(ethylmethylamino)zirconium** (TEMAZr) precursor. The performance of these devices is benchmarked against MOS capacitors utilizing other common high-k dielectrics, namely Hafnium Dioxide (HfO<sub>2</sub>) and Aluminum Oxide (Al<sub>2</sub>O<sub>3</sub>). The information presented is supported by experimental data from peer-reviewed studies, offering a valuable resource for material selection and device fabrication in advanced semiconductor research.

#### **Comparative Electrical Characterization**

The selection of a gate dielectric is critical in determining the performance and reliability of MOS devices. Key parameters include the dielectric constant (k), which influences the capacitance density, the leakage current density, which impacts power consumption and device reliability, and the interface trap density (D<sub>it</sub>), which affects the channel mobility and overall device performance. The following tables summarize the quantitative electrical properties of MOS capacitors with TEMAZr-deposited ZrO<sub>2</sub>, HfO<sub>2</sub>, and Al<sub>2</sub>O<sub>3</sub> dielectrics.

Table 1: Electrical Properties of TEMAZr-Deposited ZrO2 MOS Capacitors

| Precursor | Deposition<br>Method | Dielectric<br>Constant<br>(k) | Leakage<br>Current<br>Density<br>(A/cm²) | Interface<br>Trap<br>Density (D <sub>lt</sub> )<br>(cm <sup>-2</sup> eV <sup>-1</sup> ) | Reference |

|-----------|----------------------|-------------------------------|------------------------------------------|-----------------------------------------------------------------------------------------|-----------|

| TEMAZr    | PEALD                | 16.1 - 26.9                   | -                                        | -                                                                                       | [1]       |

Note: Specific leakage current and interface trap density values for TEMAZr-deposited ZrO<sub>2</sub> were not explicitly found in the initial search results.

Table 2: Comparative Electrical Properties of High-k Dielectric MOS Capacitors

| Dielectric<br>Material                    | Deposition<br>Method | Dielectric<br>Constant<br>(k) | Leakage<br>Current<br>Density<br>(A/cm²) | Interface<br>Trap<br>Density (D <sub>it</sub> )<br>(cm <sup>-2</sup> eV <sup>-1</sup> ) | Reference |

|-------------------------------------------|----------------------|-------------------------------|------------------------------------------|-----------------------------------------------------------------------------------------|-----------|

| ZrO <sub>2</sub><br>(TDMAZr<br>precursor) | PE-ALD               | ~24                           | -                                        | 10 <sup>10</sup> - 10 <sup>13</sup>                                                     | [2]       |

| HfO <sub>2</sub>                          | PE-ALD               | -                             | -                                        | -                                                                                       | [3]       |

| Al <sub>2</sub> O <sub>3</sub>            | PEALD                | 8.32                          | $3.08 \times 10^{-10}$ at 1V             | 1.30 x 10 <sup>13</sup>                                                                 | [4]       |

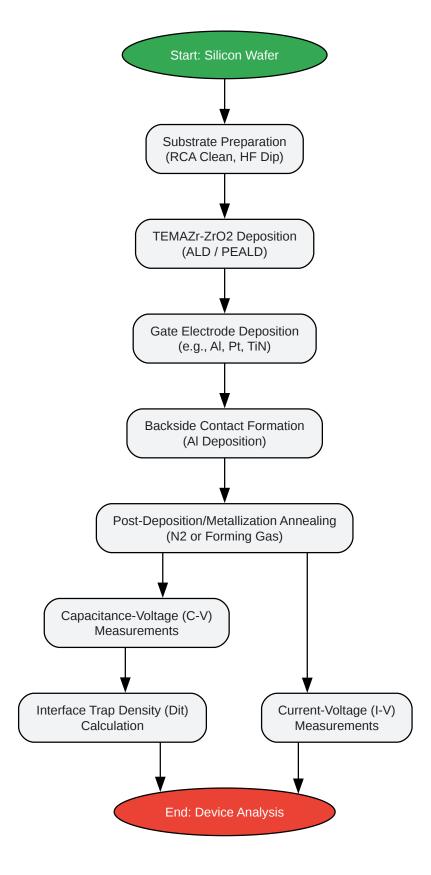

### **Experimental Protocols**

The fabrication and characterization of MOS capacitors with high-k dielectrics involve a series of precise steps. The following is a generalized experimental protocol based on common practices reported in the literature.

#### I. Substrate Preparation

- Start with a p-type or n-type silicon wafer with a specific orientation (e.g., <100>).

- Perform a standard cleaning procedure to remove organic and inorganic contaminants. A common method is the RCA clean, which involves sequential chemical baths (e.g., SC-1:

NH4OH:H2O2:H2O and SC-2: HCl:H2O2:H2O).

A final dip in a dilute hydrofluoric acid (HF) solution is often performed to remove the native oxide layer and passivate the silicon surface with hydrogen.

#### **II. High-k Dielectric Deposition (ALD/PEALD)**

- Precursor: Tetrakis(ethylmethylamino)zirconium (TEMAZr) is used as the zirconium precursor.

- Oxidant: An oxygen source, such as water vapor (H<sub>2</sub>O) for thermal ALD or an oxygen plasma

(O<sub>2</sub>) for Plasma-Enhanced ALD (PEALD), is used.

- Deposition Parameters:

- Temperature: The substrate temperature is a critical parameter and is typically maintained in a specific window (e.g., 110°C to 250°C) to ensure self-limiting surface reactions.[1]

- Pulse Times: The duration of the precursor and oxidant pulses, as well as the purge times in between, are optimized to achieve uniform and conformal film growth.

- Plasma Power (for PEALD): In PEALD, the RF power for generating the oxygen plasma is another key parameter that influences film properties.

- Process: The ALD process consists of sequential and self-limiting surface reactions. A typical cycle involves:

- Pulse of TEMAZr precursor into the reaction chamber.

- Purge with an inert gas (e.g., N₂ or Ar) to remove unreacted precursor and byproducts.

- Pulse of the oxygen source (e.g., H<sub>2</sub>O or O<sub>2</sub> plasma).

- Purge with the inert gas.

- This cycle is repeated to achieve the desired film thickness.

#### **III. Gate Electrode Deposition**

- A metal gate electrode is deposited on top of the dielectric layer.

- Commonly used metals include aluminum (AI), platinum (Pt), or titanium nitride (TiN).

- Deposition techniques such as thermal evaporation, electron-beam evaporation, or sputtering are used.

- A shadow mask is often employed to define the area of the gate electrodes.

#### IV. Backside Contact Formation

- To ensure a good ohmic contact to the silicon substrate, the native oxide on the backside of the wafer is removed.

- A metal layer, typically aluminum, is then deposited on the backside.

# V. Post-Deposition Annealing (PDA) / Post-Metallization Annealing (PMA)

- The fabricated MOS capacitors are often subjected to an annealing step to improve the quality of the dielectric and the dielectric/semiconductor interface.

- This can be a post-deposition anneal (PDA) performed after the dielectric deposition or a post-metallization anneal (PMA) performed after the gate electrode deposition.

- Annealing is typically carried out in a controlled atmosphere (e.g., nitrogen, N<sub>2</sub>, or forming gas, a mixture of N<sub>2</sub> and H<sub>2</sub>) at temperatures ranging from 300°C to 600°C.

#### VI. Electrical Characterization

- Capacitance-Voltage (C-V) Measurements:

- C-V measurements are performed using an LCR meter.

- The capacitance of the MOS capacitor is measured as a function of the applied DC gate voltage, with a small AC signal superimposed.

- Measurements are typically performed at various frequencies (e.g., 1 kHz to 1 MHz).

- From the C-V curves, parameters such as the dielectric constant, flat-band voltage (Vfb),

and oxide charge density can be extracted.

- · Current-Voltage (I-V) Measurements:

- I-V measurements are performed using a semiconductor parameter analyzer.

- The leakage current through the dielectric is measured as a function of the applied gate voltage.

- These measurements provide information about the insulating properties of the dielectric layer.

- Interface Trap Density (Dit) Extraction:

- The density of interface traps can be estimated using various techniques based on the C-V and conductance-voltage (G-V) measurements, such as the Hill-Coleman method or the conductance method.

### **Experimental Workflow**

The following diagram illustrates the logical flow of the fabrication and characterization process for MOS capacitors with TEMAZr-deposited dielectrics.

Click to download full resolution via product page

Caption: Experimental workflow for MOS capacitor fabrication and characterization.

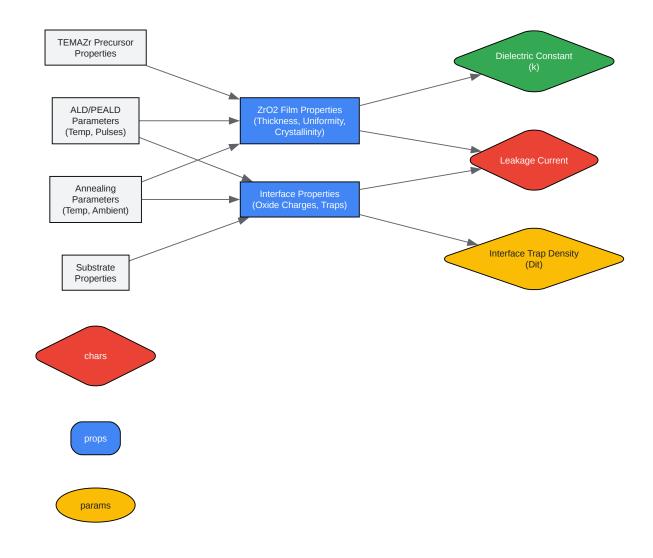

## **Signaling Pathways and Logical Relationships**

The performance of a MOS capacitor is determined by a cascade of material properties and fabrication parameters. The following diagram illustrates the key relationships influencing the final electrical characteristics.

Check Availability & Pricing

Click to download full resolution via product page

Caption: Factors influencing the electrical characteristics of MOS capacitors.

#### **Need Custom Synthesis?**

BenchChem offers custom synthesis for rare earth carbides and specific isotopiclabeling.

Email: info@benchchem.com or Request Quote Online.

#### References

- 1. researchgate.net [researchgate.net]

- 2. researchgate.net [researchgate.net]

- 3. mdpi.com [mdpi.com]

- 4. journals.ioffe.ru [journals.ioffe.ru]

- To cite this document: BenchChem. [A Comparative Guide to MOS Capacitors with TEMAZr-Deposited Zirconia Dielectrics]. BenchChem, [2025]. [Online PDF]. Available at: [https://www.benchchem.com/product/b1143060#electrical-characterization-of-mos-capacitors-with-temazr-deposited-dielectrics]

#### **Disclaimer & Data Validity:**

The information provided in this document is for Research Use Only (RUO) and is strictly not intended for diagnostic or therapeutic procedures. While BenchChem strives to provide accurate protocols, we make no warranties, express or implied, regarding the fitness of this product for every specific experimental setup.

**Technical Support:** The protocols provided are for reference purposes. Unsure if this reagent suits your experiment? [Contact our Ph.D. Support Team for a compatibility check]

Need Industrial/Bulk Grade? Request Custom Synthesis Quote

# BenchChem

Our mission is to be the trusted global source of essential and advanced chemicals, empowering scientists and researchers to drive progress in science and industry. Contact

Address: 3281 E Guasti Rd

Ontario, CA 91761, United States

Phone: (601) 213-4426

Email: info@benchchem.com