# A Comparative Guide: Btqbt-Based OFETs vs. Amorphous Silicon TFTs

Author: BenchChem Technical Support Team. Date: December 2025

| Compound of Interest |         |           |

|----------------------|---------|-----------|

| Compound Name:       | Btqbt   |           |

| Cat. No.:            | B169727 | Get Quote |

In the landscape of thin-film transistor (TFT) technologies, both organic field-effect transistors (OFETs) based on materials like dialkyl-benzothienobenzothiophene (**Btqbt**) and traditional amorphous silicon (a-Si) TFTs represent critical technologies for large-area and flexible electronics. This guide provides a comprehensive comparison of their performance, supported by experimental data and detailed fabrication protocols, to assist researchers and professionals in selecting the appropriate technology for their applications.

#### Performance Benchmark: Btqbt OFETs vs. a-Si TFTs

The choice between **Btqbt**-based OFETs and a-Si TFTs often hinges on key performance metrics such as charge carrier mobility, on/off current ratio, and threshold voltage. The following table summarizes typical performance parameters for both technologies, drawing from various research findings. It is important to note that the performance of **Btqbt** OFETs can be significantly influenced by the specific derivative (e.g., C8-BTBT, C10-DNTT) and the processing method (solution-based or vacuum deposition).

| Performance Metric      | Btqbt-Based OFETs                                                                               | Amorphous Silicon (a-Si)<br>TFTs                      |

|-------------------------|-------------------------------------------------------------------------------------------------|-------------------------------------------------------|

| Hole Mobility (µ)       | 0.1 - 12 cm²/Vs (solution-<br>processed)[1][2][3][4]; Up to 43<br>cm²/Vs (optimized devices)[3] | ~0.5 - 1 cm²/Vs[5]                                    |

| Electron Mobility (μ)   | Typically p-type, n-type<br>materials are less common<br>and have lower mobility                | ~0.5 - 1 cm²/Vs                                       |

| On/Off Current Ratio    | 10 <sup>5</sup> - 10 <sup>8</sup> [3][6][7]                                                     | 10 <sup>6</sup> - 10 <sup>7</sup>                     |

| Threshold Voltage (Vth) | -1 V to -4.3 V (can be tuned with processing)[3]                                                | 1 - 3 V                                               |

| Processing Temperature  | Room temperature to ~150°C (solution-processed); Higher for vacuum deposition                   | 180°C - 350°C (PECVD)[8]                              |

| Substrate Compatibility | Excellent with flexible plastics[6][9]                                                          | Compatible with glass and some flexible substrates[8] |

| Stability               | Good environmental stability,<br>especially DNTT derivatives[1]<br>[6][7]                       | Stable under standard operating conditions            |

### **Experimental Protocols**

Detailed methodologies are crucial for reproducing and building upon existing research. Below are generalized experimental protocols for the fabrication and characterization of both **Btqbt** OFETs and a-Si TFTs.

## Fabrication of Solution-Processed C8-BTBT OFETs (Top-Contact, Bottom-Gate)

This protocol describes a common method for fabricating **Btqbt**-based OFETs using solution-based techniques.

- Substrate Cleaning: Begin with a heavily n-doped silicon wafer with a thermally grown silicon dioxide (SiO<sub>2</sub>) layer (200-300 nm) acting as the gate dielectric. Clean the substrate by sonicating in acetone and isopropyl alcohol for 15 minutes each, followed by drying with nitrogen. An oxygen plasma treatment can be used to remove organic residues.[10]

- Dielectric Surface Treatment: To improve the interface for the organic semiconductor, treat the SiO<sub>2</sub> surface. One common method is to apply a self-assembled monolayer (SAM) of octadecyltrichlorosilane (OTS) or a polymer brush like polystyrene (PS).[10][11] For instance, a hydroxy-functionalized PS can be used to create a hydrophobic surface.[10]

- Semiconductor Deposition: Prepare a solution of a **Btqbt** derivative, such as C8-BTBT, in an organic solvent like toluene (e.g., 2.5 mg/mL).[3][12] Deposit the organic semiconductor film onto the treated substrate using techniques like spin-coating (e.g., 2500 rpm for 40 s)[3][12] or solution shearing.[10]

- Annealing: Anneal the semiconductor film to improve crystallinity and charge transport. The

annealing temperature and time depend on the specific **Btqbt** derivative and solvent used

(e.g., 80-150°C).

- Source/Drain Electrode Deposition: Deposit the source and drain electrodes on top of the organic semiconductor layer. This is typically done by thermal evaporation of gold (Au) through a shadow mask to define the channel length and width.[11][13]

- Final Annealing: A final annealing step at a moderate temperature (e.g., 50-100°C) can be performed to improve the contact between the electrodes and the organic semiconductor.

## Fabrication of Amorphous Silicon TFTs (Inverted-Staggered, Bottom-Gate)

This protocol outlines the conventional fabrication process for a-Si TFTs using plasmaenhanced chemical vapor deposition (PECVD).

Gate Electrode Deposition: Start with a glass or flexible substrate. Deposit and pattern the

gate electrode material, typically a metal like molybdenum (Mo) or chromium (Cr), using

sputtering and photolithography.

- Dielectric and Semiconductor Deposition: Sequentially deposit the gate insulator (silicon nitride, SiNx), the intrinsic amorphous silicon (a-Si:H) channel layer, and a highly doped n+ a-Si:H contact layer using PECVD.[8] The maximum process temperature during this step is typically around 180°C to 350°C.

- Channel Patterning: Use photolithography and etching to define the active channel area (the "island").[14]

- Source/Drain Electrode Deposition: Deposit and pattern a metal layer (e.g., aluminum or molybdenum) for the source and drain contacts using sputtering and photolithography.

- Contact Etching: Etch the n+ a-Si:H layer from the channel region between the source and drain electrodes.

- Passivation: Deposit a final passivation layer (e.g., SiNx) to protect the device.

- Contact Opening and Final Metallization: Open contact vias through the passivation layer and deposit the final metal interconnects.

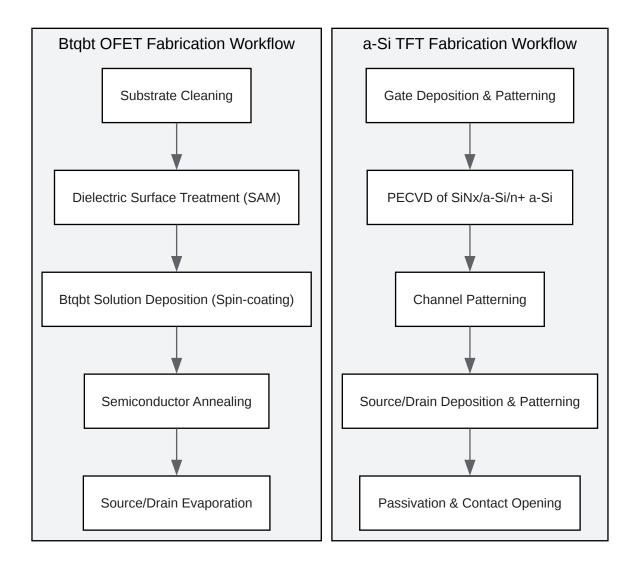

#### **Device Architecture and Fabrication Workflow**

The following diagrams illustrate the device structures and a generalized fabrication workflow for both **Btqbt** OFETs and a-Si TFTs.

Click to download full resolution via product page

Caption: Device structures of a **Btqbt** OFET and an a-Si TFT.

Click to download full resolution via product page

Caption: Generalized fabrication workflows for **Btqbt** OFETs and a-Si TFTs.

#### **Concluding Remarks**

The choice between **Btqbt**-based OFETs and a-Si TFTs is highly application-dependent. **Btqbt** OFETs, particularly solution-processed varieties, offer the promise of high-performance, low-temperature processing on flexible substrates, making them ideal for next-generation flexible and printed electronics. Their high mobility can enable faster and more complex circuits. However, variability in performance and long-term stability can still be challenges that require further research and optimization.

Amorphous silicon TFTs, on the other hand, represent a mature and highly reliable technology that dominates the current display market. Their fabrication processes are well-established, leading to high uniformity and yield over large areas. While their mobility is lower than that of high-performance OFETs, it is sufficient for many applications, including active-matrix backplanes for LCDs and OLEDs. The higher processing temperatures required for a-Si TFTs can limit the choice of flexible substrates.

For researchers and drug development professionals exploring novel sensing platforms or wearable electronics, the unique properties of **Btqbt** OFETs, such as their sensitivity to surface interactions and compatibility with flexible form factors, may be particularly advantageous. Conversely, for applications requiring proven reliability and large-scale manufacturing, a-Si TFTs remain a robust and cost-effective solution. This guide provides a foundational understanding to aid in the critical decision-making process for specific research and development endeavors.

#### **Need Custom Synthesis?**

BenchChem offers custom synthesis for rare earth carbides and specific isotopiclabeling.

Email: info@benchchem.com or Request Quote Online.

#### References

- 1. pubs.acs.org [pubs.acs.org]

- 2. High throughput processing of dinaphtho[2,3- b :2',3'- f]thieno[3,2- b]thiophene (DNTT) organic semiconductors Nanoscale (RSC Publishing) DOI:10.1039/D2NR05625A [pubs.rsc.org]

- 3. refubium.fu-berlin.de [refubium.fu-berlin.de]

- 4. High mobility solution-processed C8-BTBT organic thin-film transistors via UV-ozone interface modification Journal of Materials Chemistry C (RSC Publishing) [pubs.rsc.org]

- 5. researchgate.net [researchgate.net]

- 6. DNTTおよび関連有機半導体を用いた有機電界効果トランジスタ [sigmaaldrich.com]

- 7. fkf.mpg.de [fkf.mpg.de]

- 8. apps.dtic.mil [apps.dtic.mil]

- 9. researchgate.net [researchgate.net]

- 10. mdpi.com [mdpi.com]

- 11. researching.cn [researching.cn]

- 12. d-nb.info [d-nb.info]

- 13. m.youtube.com [m.youtube.com]

- 14. Understanding the Composition and Manufacturing Process of TFT Display Modules -Brownopto [blhlcd.com]

- To cite this document: BenchChem. [A Comparative Guide: Btqbt-Based OFETs vs. Amorphous Silicon TFTs]. BenchChem, [2025]. [Online PDF]. Available at: [https://www.benchchem.com/product/b169727#benchmarking-btqbt-ofets-against-amorphous-silicon-tfts]

#### **Disclaimer & Data Validity:**

The information provided in this document is for Research Use Only (RUO) and is strictly not intended for diagnostic or therapeutic procedures. While BenchChem strives to provide accurate protocols, we make no warranties, express or implied, regarding the fitness of this product for every specific experimental setup.

**Technical Support:**The protocols provided are for reference purposes. Unsure if this reagent suits your experiment? [Contact our Ph.D. Support Team for a compatibility check]

Need Industrial/Bulk Grade? Request Custom Synthesis Quote

### BenchChem

Our mission is to be the trusted global source of essential and advanced chemicals, empowering scientists and researchers to drive progress in science and industry. Contact

Address: 3281 E Guasti Rd

Ontario, CA 91761, United States

Phone: (601) 213-4426

Email: info@benchchem.com